# **Investigating Crosstalk in Sub-Threshold Circuits**

Mini Nanua Sun Microsystems Inc., Austin, TX Mini.Nanua@Sun.com

# David Blaauw University of Michigan, Ann Arbor, MI blaauw@eecs.umich.edu

# Abstract

Ultra-low power designs are increasingly exploiting the sub-threshold region of operation of CMOS circuits. In order to ensure correct functionality in a design, it is necessary to guarantee signal integrity. We evaluate crosstalk in an industrial microprocessor core designed in 65nm Bulk CMOS technology as the operating voltage is reduced from nominal to sub-threshold. We partition the problem into categories dictated by crosstalk analysis: crosstalk induction, crosstalk propagation and failure criterion (noise rejection curve of msff). We develop testbench circuits to study these analysis components individually. We also selected 2500 noise sensitive interconnects from the industrial microprocessor design and simulated them for crosstalk with varying operating voltages. We observe that although crosstalk injection increases in sub-threshold operation, the propagation does not, resulting in overall less crosstalk sensitive design.

#### 1. Introduction

Low performance applications that have low power requirements, are increasingly exploring the possibility of using the standard CMOS device in its sub-threshold region of operation. In sub-threshold operation the supply voltage is less than the device threshold voltage and the input capacitance is lower compared to the superthreshold operation. The combined effect of lower input capacitance and operating voltage results in low power operation. The operating current in the sub-threshold region is the sub-threshold leakage current, which results in low operating frequency of these circuits. The sub-threshold current is exponentially related to the threshold voltage and the gate voltage providing close to ideal voltage characteristic curve, a requirement for digital circuits [1]-[5].

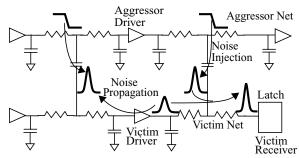

Crosstalk (noise) in a design is defined as the voltage pulse induced on a quite interconnect, the *victim* net, due to the switching activity of its neighboring

interconnects, the *aggressors* nets as shown in Figure 1. If the crosstalk voltage pulse induced on the victim corrupts a stored logic state of a latch/msff, the crosstalk event results in introducing a functional fail. The crosstalk events can also increase the delay of a logic path affecting the performance of the system. The increased delay however, is not a concern for subthreshold circuits since they tend to be low-performance. [6]-[7]

Several interconnect and device factors affect the amount of crosstalk induced on a victim net. The interconnect parameters that affect the crosstalk are: coupling capacitance  $C_{cc}$ , total capacitance  $C_t$  and resistance  $R_{net}$ . The larger the ratio of coupling capacitance to total capacitance  $(C_{cc}/C_t)$  for a victim, the more susceptible it is to crosstalk [8]. The victim resistance and the physical location of the coupling with the aggressor also affect the crosstalk. Far end coupling capacitance for instance results in higher crosstalk due to the interconnect resistance shielding effects.

Figure 1. Crosstalk

The victim/aggressor driver is defined as the group of devices which have their outputs (drain terminal) connected to the victim/aggressor respectively, i.e. these devices supply the interconnect discharging/charging currents. A small or weak victim driver results in the increase in crosstalk susceptibility. On the other hand a strong aggressor net driver would cause a fast aggressor transition inducing higher crosstalk pulse on the victim. The victim receiver is defined as the group of devices which have their input (gate terminal) connected to the victim net. The crosstalk propa-

gated across the victim receiver is a function of crosstalk pulse width and receiver output load. A large crosstalk propagation across the victim receiver can cause the interconnect driven by the receiver to be crosstalk sensitive.

The effect of device sub-threshold operation on crosstalk in a system is not known. For the same interconnect structure in a design, in sub-threshold operation the aggressor transition time would increase, therefore, it can be argued that crosstalk induced would reduce. However, the victim driver is also in sub-threshold operation which translates into weaker victim driver and hence, larger crosstalk can be induced. Also the device input capacitance, which is a part of total interconnect capacitance is smaller in sub-threshold operation making the circuit more susceptible to crosstalk. There is no previous work exploring these effects.

We study interconnects in an industrial microprocessor core designed in 65nm Bulk CMOS process for super-threshold and sub-threshold crosstalk events. We selected 2,500 noise sensitive interconnects with typical and high  $C_{cc}/C_t$  ratio to study the effect of operating voltage reduction on induced and propagated crosstalk. We observed that the crosstalk injected in sub-threshold operation is larger than in super-threshold operation. The crosstalk propagation however, is reduced in sub-threshold operation resulting in an overall less crosstalk sensitive design.

# 2. Sub-Threshold Operation

The sub-threshold operation of a device is defined as the device operating with supply voltage lower than its threshold voltage. The device current is the sub-threshold leakage current which increases exponentially with  $V_{ds}$  and  $V_{gs}$  given by:

$$I_{sub} = I_o \cdot e^{(V_{gs} - V_t)/nV_{th}} \cdot \left(1 - e^{V_{ds}/V_{th}}\right) \quad (1)$$

where,  $V_{th}$  is the thermal voltage defined as kT/q, n is the sub-threshold slope factor and  $I_o$  is defined as:

$$I_{o} = \mu_{o} C_{ox} \frac{W}{L} (n-1) V_{th}^{2}$$

(2)

The device input capacitance is a sum of the device intrinsic capacitance  $(C_i)$  and parasitic capacitance  $(C_p)$  connected in parallel [3]. The parasitic capacitance components are: overlap capacitance and fringing capacitance connected in parallel, which is similar to parasitic capacitance in super-threshold operation. The intrinsic capacitance components are oxide capaci-

tance and the depletion capacitance connected in series, given by:

$$C_i = \frac{C_{ox} \cdot C_{dep}}{C_{ox} + C_{dep}} \tag{3}$$

When compared to the super-threshold device operation where the intrinsic capacitance is  $C_{ox}$ , the intrinsic capacitance is reduced in sub-threshold operation resulting in reduction in device input capacitance.

## 3. Crosstalk

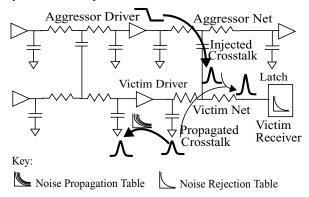

Crosstalk analysis typically involves solving the distributed RC circuit comprising of a victim, its aggressors, victim and aggressor drivers and victim receiver(s), as shown in Figure 2 [9]-[11]. The circuit is solved for both propagated and induced crosstalk. The induced crosstalk is due to the aggressor switching activity. The propagated crosstalk is due to the propagation of the crosstalk event experienced by the input net of the victim driver. The propagation through the victim driver is obtained from lookup tables stored for all circuits in the design. Typically this data is generated for the design library only once during the design cycle of a microprocessor.

Figure 2. Crosstalk Methodology

A crosstalk violation is determined if the combined induced and propagated crosstalk pulse height along a logic path in the design is larger than the noise immunity curve (noise rejection table) of the latch/msff in the design. Similar to the noise propagation table, the noise rejection tables for the design library are generated and stored as lookup tables of noise pulse height values determined to corrupt the stored value in the msff/latch. Another commonly used criterion for determining crosstalk violation is to compare the amount of propagation through every victim receiver to a crosstalk threshold (generally, circuit unity gain value). The latter criterion is obviously a more stringent one

since it does not allow for crosstalk attenuation along a logic path and results in larger number of violations.

#### 3.1 Interconnect and Driver

The interconnect parameters determining the crosstalk on a victim are: resistance ( $R_{int}$ ), total capacitance ( $C_{tot}$ ) and coupling capacitance ( $C_{cc}$ ). First order lumped approximation for crosstalk current induced in a victim is given as:

$$I_{Xtalk} = C_{cc} \cdot \frac{dV}{dt} agg \tag{4}$$

The crosstalk current is a function of the interconnect coupling capacitance and the rate at which the aggressor transitions.

The victim driver maintains a stable victim logical value, the larger the size of the driver the better its ability to dissipate the crosstalk induced current. The aggressor driver on the other hand is responsible for the aggressor transition time. A large aggressor driver would cause the aggressor to transition faster resulting in a larger crosstalk current induced on the victim. In sub-threshold operation the aggressor and the victim drivers are weak compared to their super-threshold operation. It is however not known which effect would dominate: the weak victim driver resulting in large crosstalk or the weak aggressor driver resulting in small crosstalk. These effects could also offset each other resulting in no change with respect to victim crosstalk susceptibility.

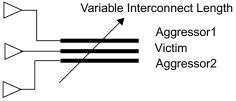

We use the testbench shown in Figure 3. The circuit

Figure 3. Testbench for Induced Crosstalk Vs. Interconnect Length

shown uses the interconnect model with distributed RC elements configured to model one victim and its two lateral aggressors on a given metal layer in a 65nm Bulk CMOS technology. The model accepts interconnect length, width, space and metal layer as variables which control the interconnect parameters: total capacitance, coupling capacitance and resistance. We use interconnect width and space values from the design rules of an industrial microprocessor in 65nm Bulk CMOS technology. We used typical interconnect lengths in the design for selected metal layer. We recorded the induced crosstalk voltage peak as a frac-

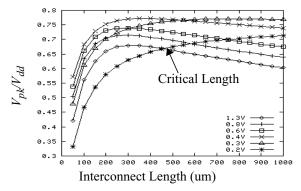

tion of supply voltage with increasing interconnect length for different operating voltages: 1.3V - 200mV as shown in Figure 4.

Figure 4. Crosstalk Induced Voltage Peak

We observe that the injected crosstalk voltage peak initially increases with reduction in operating voltage. But for operating voltages representing sub-threshold operation (less than 400mV) the injected voltage peak is lower than super-threshold operation below certain critical interconnect length, whereas increasing the interconnect length above this value results in more injected crosstalk for sub-threshold circuits.

In order to understand this effect we restate from (4) that the crosstalk current has two contributing factors: coupling capacitance and the aggressor transition time. In super-threshold operation the aggressor transition time is the dominating contributor to crosstalk but in sub-threshold operation the coupling capacitance is the dominating contributor to crosstalk. As the interconnect length is increased in our testcase the coupling capacitance between the victim and its aggressors increases. However, due to increased loading on the aggressor driver, the aggressor transition time deteriorates at the far-end of the aggressor.

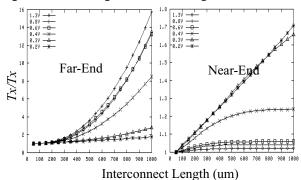

Figure 5 illustrates the near-end and far-end signal transition rate degradation for different operating voltages and increasing interconnect lengths. The x-axis is

Figure 5. Far End Aggressor Transition

the interconnect length and the y-axis is the transition degradation. The transition degradation is defined as the ratio of signal transition,  $T_x$  at a given length to signal transition for the smallest interconnect length,  $T_x$ . As shown by the plots in Figure 5, in sub-threshold operation the typical interconnect lengths considered do not have enough resistance to dominate the device resistance, therefore, we recorded similar degradation for near-end and far-end interconnect node (1.7x). However, in super-threshold operation as the interconnect length is increased we observed almost 16x degradation of signal transition at far-end, thus, off-setting the increase in coupling capacitance.

Long victim nets in a design which are susceptible to crosstalk would therefore, have a larger induced crosstalk in sub-threshold operation. Short nets however, would benefit from slow aggressor transition in sub-threshold operation.

#### 3.2 Victim Receiver

Crosstalk propagation through a victim receiver (gate) determines the crosstalk failure. If a crosstalk pulse at the gate input results in propagated crosstalk (at the output of a gate) exceeding the design required threshold it is considered a crosstalk violation. The most commonly used threshold is the unity gain point of the voltage characteristic curve of a gate. Propagated crosstalk through a gate is a function of the input crosstalk voltage height and width (in time) and the gate output loading. The wider the crosstalk pulse, the more the propagated height at the gate output. The propagation reduces with the increase in the gate output loading.

In the sub-threshold operation the injected crosstalk pulse width would be large due to slow aggressor transition and weak victim driver, the propagation would therefore be expected to increase. The victim receiver however, is also operating in sub-threshold region pointing to low propagation. We explore these effects in the following sections for a simple inverter circuit and also for a msff circuit.

# 3.2.1 Simple Gate Noise Rejection Curve

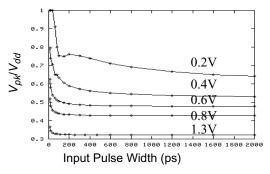

The noise rejection curve for a gate is defined as a set of crosstalk pulse heights resulting in the propagation pulse height larger than the noise threshold over a range of pulse widths. To compute the noise rejection curve of an inverter in 65nm Bulk CMOS technology, we applied a crosstalk pulse to its input. We recorded the input crosstalk voltage peak corresponding to  $10\%V_{dd}$  crosstalk voltage peak at the circuits output for a range of pulse widths. The noise rejection curves

computed are shown in Figure 6. The y-axis denotes the input crosstalk peak,  $V_{pk}$  as a fraction of operating voltage,  $V_{dd}$ . The x-axis denotes the input crosstalk pulse width at 50%  $V_{pk}$ .

The noise rejection curve shifts up as the circuit transitions from super-threshold to sub-threshold operation in Figure 6 which indicates that simple gate prop-

Figure 6. Noise Rejection Curve and  $V_{dd}$

agates lower crosstalk voltage peak in sub-threshold operation. This is essentially due to the fact that the device is faster (or alternatively has a better current drive) in super-threshold operation than sub-threshold operation. Therefore, for the same crosstalk width, it propagates a larger crosstalk voltage peak in super-threshold operation.

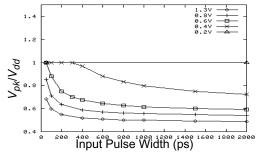

#### 3.2.2 Msff Failure

A crosstalk event in a design results in a functional failure if the storage value of a msff/latch element in the design is corrupted. The msff storage node can get corrupted if a crosstalk event on its input is captured as its clock input is in transition. We recorded the crosstalk voltage peak values on the msff input required to cause its storage node to switch from its correct logic state. These values are plotted in Figure 7 as a function of noise pulse width (x-axis). The msff circuit used for this measurement is a standard static msff design used in a 65nm Bulk CMOS industrial microprocessor. As the operating voltage is reduced the input crosstalk voltage peak required to corrupt the

Figure 7. Msff Noise Rejection Curve

msff storage node increases for the same crosstalk width. This suggests that similar to the simple gate, the super-threshold operation of a msff is more crosstalk sensitive than its sub-threshold operation. For the pulse widths considered in our example, we could not corrupt the msff stored value in subthreshold operation (200mV), i.e. the pulse height equal to  $V_{dd}$  at the input of the msff (as the clock transitions) could not change the msff state.

# 4. Crosstalk in an Industrial Design and Operating Voltage

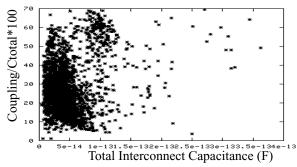

We selected 2500 nets from an industrial microprocessor core designed in 65nm Bulk CMOS technology. The criterion for selection was crosstalk sensitivity, i.e. the nets in the design close to their crosstalk threshold were selected. The nets selected have the capacitance values plotted in Figure 8. The x-axis denotes the total interconnect coupling capacitance,  $C_t$  and the y-axis denotes the ratio of interconnect coupling capacitance  $(C_{cc})$  to its total capacitance  $(C_t)$ , i.e.  $C_{cc}/C_t$ .

The scatter plot in Figure 8 illustrates that the nets selected have either long lengths (high  $C_t$ ) or large  $C_{cc}/C_t$  ratio or both. The long nets are crosstalk sensitive in super-threshold operation due to resistive shielding causing the victim driver to be less effective (Note: long aggressors in super-threshold operation induce smaller crosstalk due to aggressor transition degradation, however, long victim nets are highly susceptible to crosstalk). The nets with high  $C_{cc}/C_t$  ratio are obviously also crosstalk sensitive.

Figure 8. Interconnect Total Capacitance and Coupling Distribution

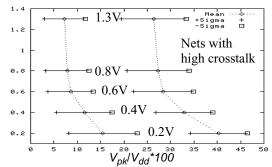

In order to determine the effect of reducing supply voltage on injected crosstalk we simulate the coupled victim-aggressors RC network with different supply voltages. The distribution of measured injected crosstalk voltage peak ( $V_{pkc}$ ) as a fraction of operating voltage ( $V_{dd}$ ) is shown in Figure 9. The x-axis is the

ratio  $V_{pk'}V_{dd}*100$  and the y-axis is the operating voltage. The plot shows the mean induced crosstalk voltage peak and its  $\pm -\sigma$  distribution with different operating voltages. For example for nominal voltage (1.3V) the

Figure 9. Injected Crosstalk Voltage Peak Distribution with Varying  $V_{dd}$

mean injected voltage peak is  $7.3\%V_{dd}$  and the +/sigma values are  $2.9\%V_{dd}$  and  $11.7\%V_{dd}$ , respectively. The mean crosstalk voltage peak increases for subthreshold operation to  $15.5\%V_{dd}$ . We also show the distribution for 317 nets with high crosstalk in a separate plot in Figure 9 to show the mean crosstalk injected voltage increases by 2x in sub-threshold operation. The injected noise in our selected interconnects, therefore increased with sub-threshold operation.

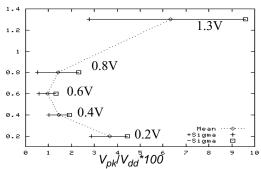

The propagated crosstalk voltage peak distribution is shown in Figure 10. The x-axis is the propagated

**Figure 10.** The Propagated Crosstalk Voltage Peak Distribution with Varying  $V_{dd}$

voltage peak as a percent of supply voltage  $(V_{pk}/V_{dd}*100)$ . The y-axis is the supply voltage. For example, for nominal voltage the mean propagated peak is  $6.34\%V_{dd}$  whereas for subthreshold supply voltage (200mV) the mean propagated peak is  $3.6\%V_{dd}$ . As expected the mean voltage peak reduces as the operating voltage is reduced. However, the trend does not extend to true sub-threshold operating voltages, and the mean crosstalk propagated voltage increases (although its still lower than true super threshold operation). This increase is due to the increase in injected crosstalk

width with sub-threshold operation.

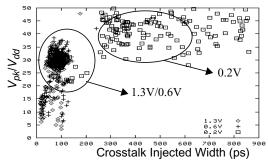

The injected crosstalk width with operating voltage is plotted (for top 317 noise sensitive interconnects) in Figure 11. The x-axis represents the crosstalk injected width. The y-axis represents the crosstalk peak w.r.t. operating voltage. The plot shows that for the same set of interconnects, as the supply voltage is reduced to sub-threshold operation, the injected voltage width increases appreciably.

In our testcircuit crosstalk propagation, i.e. noise rejection curve measurements in Section 3.2, we observed smaller propagation for sub-threshold operation as long as the crosstalk widths are similar. However, in the design, for similar nets, the sub-threshold operation results in the injected crosstalk with larger widths than super-threshold operation. And since crosstalk propagation increases with crosstalk width, as the operating voltage decreases we see an initial decrease in propagation followed by an increase.

**Figure 11.** The Injected Crosstalk Pulse with Varying  $V_{dd}$

The number of interconnects violating crosstalk criterion in the design with varying  $V_{dd}$  are listed in Table 1, as expected the super-threshold operation creates crosstalk violations while the sub-threshold operation has no crosstalk violations.

**Table 1:** Crosstalk Violations

| Total Nets | Violations |      |      |      |      |

|------------|------------|------|------|------|------|

|            | 1.3V       | 0.8V | 0.6V | 0.4V | 0.2V |

| 2500       | 20         | 1    | 0    | 0    | 0    |

### 5. Conclusion

We investigated the sub threshold operation of a design for crosstalk effects. We used testbench circuits from an industrial processor designed with 65nm Bulk CMOS technology. We make the following observations:

Crosstalk Injection: the sub-threshold operation results in higher crosstalk voltage peaks and widths for noise sensitive long interconnects.

- 2. Crosstalk Propagation: the sub-threshold operation results in relatively less propagated crosstalk voltage peak.

- 3. Failure Criterion: the noise rejection curves for simple gates and msff circuits shift to higher crosstalk voltage peaks, i.e. larger input crosstalk peak is required to cause a violation.

Combining all components of crosstalk, in our experiment, we found the sub-threshold operation to have fewer violations than super-threshold operation for similar noise sensitive interconnects in a design.

# 6. References

- [1] B.H. Calhoun and A. Chandrakasan, "Modeling and Sizing for Minimum Enery Operation in Subthreshold Circuits", *IEEE Journal of Solid-State Circuits*, Vol. 40, NO. 9, Sep 2005, pp. 1778-1786.

- [2] S. Hanson et. al., "Ultralow-voltage minimum-energy CMOS", *IBM Journal of Research and Development*, Allen Press, Jul./Sep. 2006, pp. 1-22.

- [3] B.C. Paul, A. Roychowdhury, and K. Roy, "Device Optimization for Ultra-Low Power Digital Sub-Threshold Operation", *ISLPED*, Aug 2004, pp. 96-101.

- [4] J. Chen, L.T. Clark, and Y. Cao, "Robust Design of High Fan-In/Out Subthreshold Circuits", *IEEE Proceedings ICCD*, 2005.

- [5] M.D. Godfrey, "CMOS Device Modeling for Subthreshold Circuits", *IEEE Transactions on Circuits and Systems*, Vol. 39, Aug 1992, pp.532-539.

- [6] F. Caiget, S. Delamas-Bendhia and, E. Sicard, "The Challenge of Signal Integrity in Deep-Submicronmeter CMOS Technology", *IEEE Proceedings*, Vol. 89, April 200, pp.556-573.

- [7] P. Heydari and, M. Pedram, "Capacitive Coupling Noise in High-Speed VLSI Circuits", *IEEE Transactions CAD*, Vol.24, 2005.

- [8] T. Sakurai, "Closed-Form Expressions for Interconnect Delay, Coupling, and Crosstalk in VLSI's", *IEEE Transactions on Electron Devices*, Jan 1993, pp. 118-124.

- [9] K.L. Shepard, "Harmony: Static Noise Analysis of Deep Submicron Digital Integrated Circuits", *Transactions IEEE CAD*. Vol.18, 1999.

- [10] R. Levy, et.al., "ClariNet: A Noise analysis tool for deep submicron design", *DAC*, 2000, pp. 233-238.

- [11] W. Che, S.K. Gupta and M.A. Breuer, "Analytical Models for Crostalk Excitation and Propagation in VLSI Circuits", *IEEE Transactions on CAD of Integrated Circuits and Systems*, Oct 2002, pp. 1117-1131.