# A 5.58 nW Crystal Oscillator Using Pulsed Driver for Real-Time Clocks

Dongmin Yoon, Member, IEEE, Taekwang Jang, Dennis Sylvester, Fellow, IEEE, and David Blaauw, Fellow, IEEE

Abstract-A 5.58 nW real-time clock using a crystal oscillator is presented. In this circuit, the amplifier used in a traditional circuit is replaced with pulsed drivers. The pulse is generated with precise timing using a DLL. With this approach, an extremely low oscillation amplitude of 160 mV results in low-power operation. This low-amplitude oscillation is sustained robustly using additional supply voltages: a lower supply for the final drive stage and a higher supply used for pulses that drive the final drive stage, which ensures low ON-resistance necessary for reliable operation. The different supply levels are generated on-chip by a switched capacitor network (SCN) from a single supply. The circuit has been tested at different supply voltages and temperatures. It shows a minimum power consumption of 5.58 nW and power supply sensitivity of 30.3 ppm/V over supply voltage of 0.94-1.2 V, without degrading the crystal's temperature dependency: between -20 °C and 80 °C. Moreover, its performance as a real-time clock has been verified by measurement of an Allan deviation of  $1.16 \times 10^{-8}$ .

*Index Terms*—Crystal oscillator, low power, pulsed driver, realtime clock, wireless sensor node.

# I. INTRODUCTION

**B** ELL'S law of computing classes [1] states that approximately every decade, a new computer class with lower price and volume replaces the previous class. Extending this prediction to the next decade, the next computing class is expected to have a size that is orders of magnitude smaller than today's cell phones. One of the best examples of the next computing class is the wireless sensor node. With significant computing power packed within a small volume and lower cost thus the term *smart dust* [2]—it has the potential to change how people interact with the environment. However, many issues still remain to be solved, which have been the focus of active research to realize wireless sensor nodes and use them for continuous monitoring devices [3], [4]. Possibly, the most significant challenge rises from limited power and energy budgets.

For wireless sensor nodes, the volume that can be allocated to the battery is orders of magnitude smaller than a cell phone [2]. In some applications, the system does not have any battery and operates directly from an energy harvester [5] or is wirelessly coupled to a power source, severely limiting the power budget of the different circuit blocks. One of the key building blocks

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2015.2501982

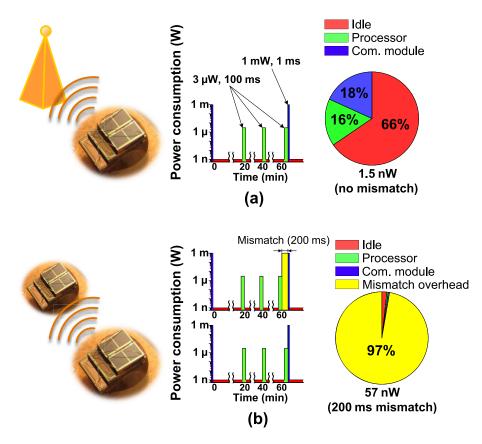

in a sensor node system is the real-time clock, which keeps track of the wall-clock time. The power budget and accuracy requirement of a real-time clock depends on the sensor node use scenario. Under one typical scenario, shown in Fig. 1(a), a processor is activated every 20 min to take a measurement which could take 100 ms at 3 µW. Then, once every hour, the processor transmits this data to a base station, requiring  $\sim 1 \text{ ms}$ at 1 mW. For the remainder of the time, the whole system will be put into sleep mode where it will consume only idle power, which has been shown to have a limit as low as  $\sim 1 \text{ nW}$  [4]. Since the base station is supplied with power from a wired source (e.g., a wall plug), it can listen for a transmitted signal continuously. Hence, the sensor nodes do not have an extremely high timing accuracy requirement, and an on-chip timer that consumes as little as 0.66 nW with an average random error of 200 ms over an hour [6] can be used, providing for an extremely low-power system that can be highly miniaturized.

However, for some applications, sensor nodes have to communicate with each other. In such a scenario, these nodes will have synchronized timing references, and two nodes will transmit and receive data when they are notified by their timing references to do so. Unfortunately, two independently operating timing references will suffer from mismatch because of random behaviors such as jitter. This scenario is shown in Fig. 1(b). Given a silicon-based timing reference, operating in sub-nW range such as the 0.66 nW timer in [6], two nodes are expected to have a random mismatch of 200 ms in an hour due to the high-frequency instability which corresponds to 56 ppm in an hour. In this case, the RF communication module of one node will be activated earlier than the other and has to wait until the second node comes online before it can initiate communication. During this mismatch time window, the RF module consumes substantial energy, which comes to dominate the total power consumption as shown in Fig. 1(b) and increases the average power consumption to 57 nW, which is 38 times larger than the previous case.

To avoid this high energy loss during timer mismatch, each node must be equipped with a high accuracy timing source. Crystal oscillators (XO) provide a more constant frequency than silicon-based timers; however, they usually consume much higher power than an ultra-low-power sensor node system, typically in the range of  $\mu$ W to hundreds of nW.

To address these issues, this paper proposes a new XO topology that lowers power consumption while maintaining the crystal's frequency stability. A novel pulse charge injection scheme realized by a DLL is introduced to replace the traditional amplifier. Furthermore, extremely low oscillation amplitude of 160 mV is realized, which results in low-power

0018-9200 © 2015 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

Manuscript received April 13, 2015; revised October 02, 2015; accepted November 11, 2015. Date of publication January 01, 2016; date of current version January 29, 2016. This paper was approved by Associate Editor Ken Suyama.

The authors are with the University of Michigan, Ann Arbor, MI 48109 USA (e-mail: dmyoon@umich.edu).

Fig. 1. Operation scenarios of WSN. (a) Node-to-base station communication. (b) Node-to-node communication with mismatch.

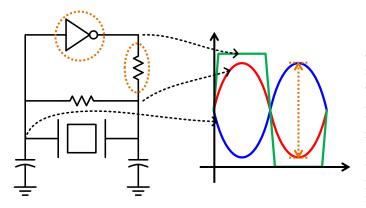

Fig. 2. Conventional XO circuit and waveform.

operation. This low-amplitude oscillation is sustained robustly using two supply voltages: 1) a lower supply, which is used for the final drive stage, and 2) a higher supply, which is used to generate the pulses that drive the final drive stage. An on-chip switched capacitor network (SCN) generates multiple levels of voltage to operate different parts of the circuit for optimum power and performance.

This paper is structured as follows. Section II discusses prior works. Section III introduces the proposed topology for the XO and its operating principle. Section IV discusses the theory of the proposed XO circuit operation. Section V discusses each circuit block in detail. Section VI presents measurement results of the test chip. Finally, Section VII concludes this work.

#### **II. PREVIOUS WORKS**

To analyze the issues with a conventional XO driver topology, the basic configuration is shown in Fig. 2. An inverter in closed loop amplifies noise at its input to kick-start the oscillation. At the same time, it provides a 180° phase shift and generates lost energy each period to maintain crystal oscillation. For this configuration, inverter gain is uncontrolled. As a result, the inverter output is clipped and a square wave is generated. To avoid this, a series resistor at the output is introduced to control the drive level. A crystal driven at prohibitively high power levels-called the overdrive level-is known to suffer from reliability issues, which degrades frequency stability and sometimes leads to oscillation at higher overtone. This resistor also forms a low-pass filter with the capacitor which avoids the crystal oscillating at higher overtone frequencies. However, there are three noticeable sources of power loss in this circuit. 1) The driver itself consumes significant static power. Because its input signal is a sinusoidal wave, the driver is never completely turned OFF, which results in static current. 2) Uncontrolled gain of the inverter produces high oscillation amplitude, which leads to increased power loss by the crystal itself in each cycle. 3) The series resistor dissipates energy since the difference between square wave at the driver output and sine wave oscillation at the crystal is dissipated by this resistor. Overall, this configuration will typically consume power in hundreds of nW to a couple of  $\mu$ W for a 32.768 kHz crystal. While power consumption can be reduced by lowering supply voltage, there is a lower bound

Fig. 3. Overview of widely used low-power XO circuit.

on how much the supply voltage can be reduced in this topology due to the following fundamental dependency. Smaller oscillation leads to smaller input signal to the driver. This smaller oscillation input makes the driver weaker which requires a larger driver and careful selection of design parameters to sustain the oscillation. As the oscillation drops below the threshold voltage of the inverter transistors, the drive strength increases very rapidly, restricting oscillation amplitude to higher, super threshold voltages with associated higher power levels.

To cope with this problem, a novel circuit was proposed in [7] and [8], which is shown in Fig. 3. This circuit monitors the oscillation amplitude and controls the bias current of the driver. Using an active feedback control loop, this approach can reduce driver current, which reduces oscillation amplitude and eliminates the need for a series resistor. The lowest power consumption reported using this scheme with a 32.768 kHz crystal is 27 nW from the oscillation alone, and 32 nW including the output buffer to generate a full-swing signal [9]. More recent work using this scheme is introduced in [10], which consumes 38.4 nW using a 50 kHz crystal in a 130 nm process. However, this level is still larger than the standby power consumption of the whole system in an ultra-low-power WSN application [4], [11]. The power consumption in this topology is due to the following reasons. 1) Although smaller than the conventional circuit, the driver still dissipates static bias current. 2) The topology still requires a high-supply voltage and significant power is dissipated in the current mirror transistors. 3) The closed-loop control system including the amplitude monitoring circuit which made the 27 nW oscillation power possible, consumes significant power itself. Furthermore, the oscillation amplitude is controlled by device sizing in the current mirror loop, which requires good device matching. Therefore, to accommodate process variation, the system requires significant margin in transistor size to ensure robust operation over a wide range of operating conditions, especially as the voltage amplitude reduces and transistors operate in the subthreshold region. This in turn increases the minimum oscillation voltage.

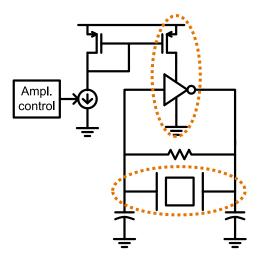

Fig. 4. Preamplifier concept of the proposed circuit.

### III. PROPOSED APPROACH

To further reduce the power consumption of an XO, we propose a new circuit topology which uses a preamplifier concept, which is the first of two key components for the proposed circuit. Considering again the conventional circuit with only a single inverter in Fig. 2, a preamplifier is placed before the output driver as shown in Fig. 4. A new  $V_{DD}$  ( $V_{DDL}$ ) and ground (V<sub>SSL</sub>) pair-which will be called low-voltage supplysmaller than the nominal  $V_{DD}$  ( $V_{DDH}$ ) and ground ( $V_{SSH}$ ) pair is supplied, so that oscillation amplitude is kept small. Then, a larger voltage is supplied to the preamplifier, so that the small input signal is amplified before being applied to the output driver. This provides the output driver with maximum gateto-source voltage, minimizing ON-resistance of the transistor and supports immediate transfer of energy to the oscillation with minimum loss in the transistor. This supply voltage pair is referred to as the high-voltage supply. In this configuration, the smaller oscillation amplitude no longer weakens the driver. With the help of the higher input signal to the driver, it now has very low ON-resistance and can maintain oscillation robustly, even at very small low-voltage supply. In addition, the driving transistor now operates in the linear region instead of subthreshold region, which helps to cope with PVT variation better. In addition, the ON-resistance is less dependent on  $V_{\rm DS}$  and hence oscillation amplitude. With boosted  $V_{\rm GS}$ , the ONresistance remains low even when oscillation amplitude  $(V_{DS})$ is reduced, which is important for maintaining stable oscillation when oscillation amplitude is reduced.

This approach, however, has two remaining issues that need to be addressed. If the preamplifier is implemented using an operational amplifier with enough bandwidth, the preamplifier alone will consume a bias current larger than 10 nA at given process technology. Moreover, the amplified signal tends to make the output driver too strong, so that it again requires a series resistor to suppress higher tones. To address these issues, a pulsing scheme is implemented-the second key idea of the proposed circuit. The operational amplifier previously discussed is replaced with an inverter and a pulse generator (PG). Instead of prematurely turning ON the driver and perturbing the sinusoidal oscillation, the driver is turned ON only at each oscillation peak to regenerate energy only when it is needed. Precise timing is controlled by a DLL locked to the crystal's resonant frequency. Pulses can be generated at preferred timing with the DLL and these signals are used to separately drive

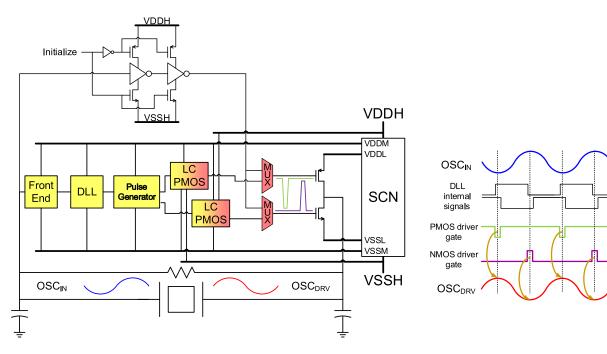

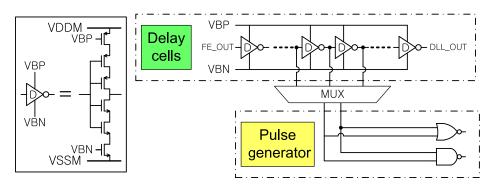

Fig. 5. Block diagram of the proposed circuit.

NMOS and PMOS drivers. For example, at oscillation maxima, the PMOS will turn ON briefly and clamp the oscillation's top voltage excursion level back to  $V_{DDL}$ . At minima, the NMOS will turn ON and clamp the bottom voltage level down to  $V_{SSL}$ .

The proposed scheme injects current when the XO node voltage is close to the low-supply voltages. Therefore, it can sustain stable oscillation without a series resistor and with a small voltage drop across the drive transistor, which reduces power dissipation of the driver. In addition, only one transistor of the driver is ON at a time while keeping  $V_{\rm GS}$  of the other transistor reverse-biased. This removes any need for static bias current, thus significantly reducing the output driver power.

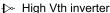

If DLL and pulse generation circuits are run in high-voltage supply, the power consumption in these circuits will become dominant and negate the benefit from lower driver power. Therefore, another voltage pair— $V_{\text{DDM}}$  and  $V_{\text{SSM}}$ —in between high- and low-voltage supplies is introduced, which is referred to as the medium voltage supply. By keeping the mediumvoltage supply at near-threshold level, power consumption of DLL and other circuits is kept low. Since the output driver still requires a high-amplitude signal at its input, level converters are implemented between the DLL/PGs and the driver stage. For converting the low-voltage crystal oscillation amplitude to the medium-voltage supply level, a body-biased inverter front end (FE) is used.

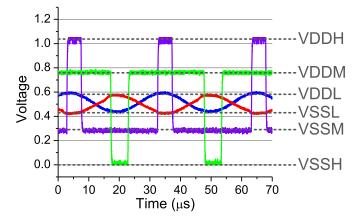

The block diagram and waveform for the resulting circuit is shown in Fig. 5. Overall, the circuit will maintain the oscillation as follows. Once the DLL is locked to the crystal's resonant frequency, the DLL generates a set of 32.768 kHz square waves with different phases. The circuit picks a pair of these square waves and produces a precise pulse with a predefined timing. Then, these pulses are applied at output driver to inject energy at oscillation peak and thereby sustain the oscillation.

As a result of the multitiered supply approach, four extra supply voltages are needed. For practical application, these

Fig. 6. Lumped model of crystal oscillator using pulsed driver.

voltages should be generated efficiently on-chip. In this circuit, an on-chip SCN is used to generate all needed voltage and the overall circuit operates from just one supply  $V_{DD}$  and ground.

#### IV. THEORY OF OPERATION

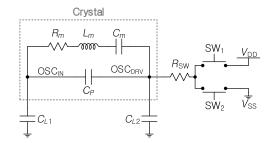

This section presents a more detailed explanation of the circuit operation and its behavior as a function of transistor size (ON-resistance), pulse width, and pulse location. The pulsed driver replaces an inverter in conventional circuit and provides  $180^{\circ}$  of phase shift. In fact, the output driver of the proposed circuit is identical to a regular inverter structure, although its operation is duty-cycled to achieve considerable power reduction. The crystal and load capacitance provide an additional  $180^{\circ}$  of phase shift, meeting the phase requirement for oscillation. Therefore, we will focus our discussion in this section on how energy is maintained through pulsed driver operation. Fig. 6 shows a theoretical model of a crystal oscillator using a pulsed driver.  $R_m$ ,  $L_m$ ,  $C_m$ , and  $C_p$  comprise the electrical model of a quartz crystal.  $C_{L1}$  and  $C_{L2}$  represent load capacitances that are assumed to be matched and equal. Note that the bias resistor that is present in Figs. 4 and 5 have been removed for simplicity since its only purpose is providing the

Fig. 7. Simplified passive networks.

Fig. 8. Abstract waveforms of crystal oscillation. (a) Ideal switches. (b) Switches with non-zero on-resistance.

correct bias voltage at OSC<sub>IN</sub>. At the oscillation peak, one of the two switches is turned ON for a duration of  $T_{ON}$ . Note that  $T_{ON}$  is centered at the peak voltage in this analysis.  $R_{SW}$  represents switch resistance. In a practical realization, the switch is implemented with a transistor, which will have a small drainto-source voltage and will operate in the linear region, so the switch is well approximated by  $R_{SW}$ . Further, for simplicity, all voltages are measured in reference to  $V_{SS}$ .

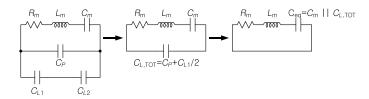

For an initial analysis, we consider only the passive network and assume the switches are not operating (Fig. 7). The crystal is assumed to be resonating in steady state, with voltage at OSC<sub>IN</sub> and OSC<sub>DRV</sub>, each oscillating (180° out of phase to each other) with a peak-to-peak voltage of  $V_{OSC}$  due to this resonance. Reducing the two-load capacitors  $C_{L1}$ ,  $C_{L2}$ , and  $C_p$  as  $C_{L,TOT}$ , we can see that the voltage across  $C_{L,TOT}$  is oscillating at an amplitude of  $V_{OSC}$ . Now, we combine  $C_{L,TOT}$  together with  $C_M$  as  $C_{eq}$ , which is given as

$$C_{\text{eq}} = C_m \| C_{L,\text{TOT}} = C_m \| (C_p + C_{L1}/2).$$

(1)

Resonance frequency  $F_{OSC}$  can then be approximated with reasonable accuracy as

$$F_{\rm OSC} = \frac{1}{2\pi\sqrt{L_m C_{\rm eq}}}.$$

(2)

At this condition, the oscillation amplitude of the voltage across capacitor  $C_m V_{Cm,amp}$  is given by

$$V_{Cm,\text{amp}} = V_{\text{OSC}} \cdot \frac{C_{L,\text{TOT}}}{C_m}.$$

(3)

Oscillation amplitude for the current in inductor  $L_m I_{Lm,amp}$  can be calculated by equating the maximum energy stored in the inductor to the maximum energy stored in the capacitor

$$I_{Lm,\text{amp}} = (V_{Cm,\text{amp}} + V_{CL,\text{TOT},\text{amp}}) \cdot \sqrt{\frac{C_{\text{eq}}}{L_m}}$$

$$= V_{\text{OSC}} \cdot \left(1 + \frac{C_{L,\text{TOT}}}{C_m}\right) \cdot \sqrt{\frac{C_{\text{eq}}}{L_m}}.$$

(4)

Therefore, we can calculate average power loss from the crystal's resistive component  $P_{\text{loss}}$  and energy loss per cycle from this resistive component  $E_{\text{loss}}$  as

$$P_{\text{loss}} = 0.5 \cdot I_{Lm,\text{amp}}^2 \cdot R_m$$

$$E_{\text{loss}} = \frac{P_{\text{loss}}}{F_{\text{OSC}}} = \frac{1}{2 \cdot F_{\text{OSC}}} \cdot \frac{R_m C_{\text{eq}}}{L_m} \cdot \left(1 + \frac{C_{L,\text{TOT}}}{C_m}\right)^2$$

$$\cdot V_{\text{OSC}}^2 = \pi \sqrt{L_m C_{\text{eq}}} \cdot \frac{R_m \cdot C_{\text{eq}}}{L_m} \cdot \left(\frac{C_{L,\text{TOT}}}{C_{\text{eq}}}\right)^2$$

$$\cdot V_{\text{OSC}}^2 = \frac{\pi R_m C_{L,\text{TOT}}^2 V_{\text{OSC}}^2}{\sqrt{L_m C_{\text{eq}}}}.$$

(6)

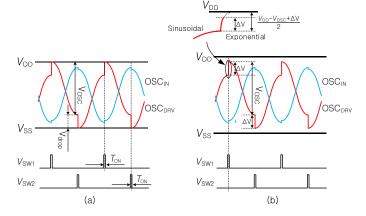

In order to sustain a steady oscillation, the switches regenerate the energy lost during the oscillation, i.e.,  $E_{\rm loss}$  at a given oscillation amplitude must equal the energy delivered by the switches from the power supplies. Given an initial rail-to-rail oscillation of  $V_{\rm OSC} = V_{\rm DD}$  and switches that are turned ON at oscillation peaks for a short duration, no energy is transferred to the passive network since there is no voltage across  $R_{\rm sw}$ . However, on the following oscillation period,  $V_{\rm OSC}$  will degrade by some voltage drop  $V_{\rm drop}$ , resulting in  $V_{\rm OSC} = V_{\rm DD} - V_{\rm drop}$ .

For an initial analysis, it is assumed that  $R_{SW} = 0$  and  $T_{ON}$  is very short. When SW<sub>1</sub> is turned ON, it charges node OSC<sub>DRV</sub> to  $V_{DD}$  instantly. Due to very narrow frequency bandwidth of  $R_m - L_m - C_m$  connection, the inductor current is not perturbed significantly by this event. Therefore, current from  $V_{DD}$  flows into the capacitor network formed by  $C_{L1}$ ,  $C_{L2}$ , and  $C_p$ . Seen from the switches, the equivalent input capacitance  $C_{eq,sw}$  is given as

$$C_{\rm eq,sw} = C_{L2} + (C_{L1} \| C_p).$$

<sup>(7)</sup>

One half cycle after this transition, SW<sub>2</sub> is turned ON to discharge OSC<sub>DRV</sub> to  $V_{SS}$ . These switching operations cause the dc levels to shift as shown in Fig. 8(a) with minimal perturbation to the resonant behavior of the crystal (i.e., the current through  $L_m$ ). Therefore, the voltage at the OSC<sub>DRV</sub> node shows a dc shift of  $V_{drop}$  at each switching operation followed by a half sine wave with peak-to-peak amplitude of  $V_{OSC}$  as seen in Fig. 8(a).

These switching sequences cause a change in the energy level stored on  $C_{eq,sw}$ . We will refer to this change of energy in each oscillation cycle as  $E_{regen}$ . It can be calculated as follows:

$$E_{\text{regen}} = \frac{1}{2} \cdot C_{\text{eq,sw}} \cdot \left[ V_{\text{DD}}^2 - (V_{\text{DD}} - V_{\text{drop}})^2 \right] - \frac{1}{2} \cdot C_{\text{eq,sw}} \cdot V_{\text{drop}}^2 = C_{\text{eq,sw}} \cdot (V_{\text{DD}} - V_{\text{drop}}) \cdot V_{\text{drop}}.$$

(8)

Steady state is reached when  $E_{\text{regen}}$  in (8) is equal to  $E_{\text{loss}}$ in (6), with  $V_{\text{DD}}$  in the equation replaced by  $V_{\text{OSC}} = V_{\text{DD}} - V_{\text{drop}}$ . For example, with  $R_m = 30 \text{ k}\Omega$ ,  $L_m = 10.2 \text{ kH}$ ,  $C_m = 2.3129 \text{ fF}$ , and  $C_p = 1.5 \text{ pF}$ ,  $C_{L1} = C_{L2} = 20 \text{ pF}$ ,  $V_{\text{DD}} = 1.5 \text{ pF}$ ,  $C_{L1} = C_{L2} = 20 \text{ pF}$ ,  $V_{\text{DD}} = 1.5 \text{ pF}$ ,  $C_{L1} = C_{L2} = 20 \text{ pF}$ ,  $V_{\text{DD}} = 1.5 \text{ pF}$ ,  $C_{L1} = C_{L2} = 20 \text{ pF}$ ,  $V_{\text{DD}} = 1.5 \text{ pF}$ ,  $C_{L1} = C_{L2} = 20 \text{ pF}$ ,  $V_{\text{DD}} = 1.5 \text{ pF}$ ,  $C_{L1} = C_{L2} = 20 \text{ pF}$ ,  $V_{\text{DD}} = 1.5 \text{ pF}$ ,  $C_{L1} = C_{L2} = 20 \text{ pF}$ ,  $V_{\text{DD}} = 1.5 \text{ pF}$ ,  $C_{L1} = C_{L2} = 20 \text{ pF}$ ,  $V_{\text{DD}} = 1.5 \text{ pF}$ ,  $C_{\text{DD}} = 1$

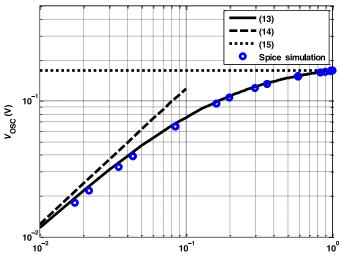

10 T 10 Y 10 Y 10 Y To  $\gamma$ Fig. 9. Simulation and analytic solution of oscillation amplitude when  $R_m = 30 \text{ k}\Omega$ ,  $T_{\text{ON}} = 200 \text{ ns}$ ,  $L_m = 10.2 \text{ kH}$ ,  $C_m = 2.3129 \text{ fF}$ , and  $C_p = 1.5 \text{ pF}$ ,  $C_{L1} = C_{L2} = 10 \text{ pF}$ ,  $V_{\text{DD}} = 180 \text{ mV}$ .

(16) (17)

(18)

Spice simulation

10<sup>6</sup>

$R_{SW}$  ( $\Omega$ ) Fig. 10. Effect of  $R_{SW}$  on the energy consumption per cycle when  $R_m = 30 \text{ k}\Omega$ ,  $T_{ON} = 200 \text{ ns}$ ,  $L_m = 10.2 \text{ kH}$ ,  $C_m = 2.3129 \text{ fF}$ , and  $C_p = 1.5 \text{ pF}$ ,  $C_{L1} = C_{L2} = 10 \text{ pF}$ ,  $V_{DD} = 180 \text{ mV}$ .

10<sup>5</sup>

10<sup>4</sup>

180 mV,  $V_{drop}$  and  $V_{OSC}$  are 19.3 and 160.7 mV, respectively.  $P_{loss}$  and  $E_{loss}$  are 2.17 nW and 66.3 fJ, respectively. For lower  $C_{L1}$  of 10 pF,  $V_{drop}$  decreases to 12.2 mV and  $P_{loss}$  reduces to 0.757 nW. At C<sub>L1</sub> of 5 pF,  $V_{drop}$  is 8.7 mV and  $P_{loss}$  reduces to 0.299 nW.

While the inclusion of  $SW_2$  effectively removes energy from the passive network, this process is essential to sustain the oscillation. With only  $SW_1$  operating, the dc level of oscillation converges to  $V_{DD}$ . This makes the energy regeneration process via  $SW_1$  less efficient, eventually causing the oscillation to diminish and cease completely. This would also pose a practical challenge, since the circuit would have a rising dc level of oscillation.

We now turn our attention to the energy supplied from  $V_{\text{DD}}$ ( $E_{V\text{DD}}$ ) and regeneration efficiency  $\xi$ . Part of the supplied

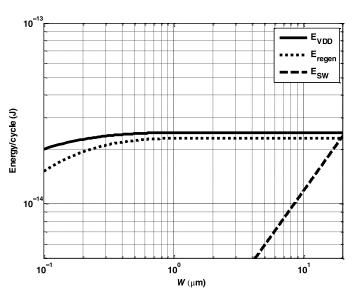

Fig. 11. Effect of W on the energy consumption per cycle when  $R_m = 30 \text{ k}\Omega$ ,  $T_{\text{ON}} = 200 \text{ ns}$ ,  $L_m = 10.2 \text{ kH}$ ,  $C_m = 2.3129 \text{ fF}$ , and  $C_p = 1.5 \text{ pF}$ ,  $C_{L1} = C_{L2} = 10 \text{ pF}$ ,  $V_{\text{DD}} = 180 \text{ mV}$ .

energy is dissipated in  $R_{sw}$ , causing efficiency to degrade. These terms are calculated as follows:

$$E_{VDD} = C_{eq,sw} \cdot V_{DD} \cdot [V_{DD} - (V_{DD} - V_{drop})]$$

=  $C_{eq,sw} \cdot V_{DD} \cdot V_{drop}$  (9)

$E_{docs} = E_{regen} = V_{DD} - V_{drop}$

$$\xi = \frac{E_{\text{loss}}}{E_{\text{VDD}}} = \frac{E_{\text{regen}}}{E_{V\text{DD}}} = \frac{V_{\text{DD}} - V_{\text{drop}}}{V_{\text{DD}}}.$$

(10)

Note that although a larger  $V_{drop}$  leads to less  $E_{loss}$  in the crystal, it incurs more overhead in the circuit and leads to lower efficiency.

When the resistance of the switches is considered, the oscillation amplitude will be reduced as shown in Fig. 8(b). When the switches are OFF,  $OSC_{DRV}$  makes a half cycle transition of  $V_{OSC}$ . Then, one of the switches is turned ON which charges or discharges the voltage by  $\Delta V$  assuming the resistance of SW1 and SW2 are equal. As the inductor current is not significantly perturbed by the switching event, the capacitor network  $C_{eq,sw}$ is connected to either  $V_{DD}$  or  $V_{SS}$  through the switch resistance  $R_{sw}$ . Therefore, the charging voltage  $\Delta V$  can be expressed as an exponential curve as the following equation:

$$\Delta V = \frac{V_{\rm DD} - V_{\rm OSC} + \Delta V}{2} \left( 1 - e^{-\frac{T_{\rm ON}}{R_{\rm SW}C_{\rm eq,sw}}} \right)$$

$$= \frac{V_{\rm DD} - V_{\rm OSC} + \Delta V}{2} \gamma$$

$$\Delta V = \frac{\gamma}{2 - \gamma} \left( V_{\rm DD} - V_{\rm OSC} \right)$$

$$= \frac{1 - e^{-\frac{T_{\rm ON}}{R_{\rm SW}C_{\rm eq,sw}}}}{1 + e^{-\frac{T_{\rm ON}}{R_{\rm SW}C_{\rm eq,sw}}}} \left( V_{\rm DD} - V_{\rm OSC} \right)$$

$$= \tanh \left( \frac{T_{\rm ON}}{2R_{\rm SW}C_{\rm eq,sw}} \right) \left( V_{\rm DD} - V_{\rm OSC} \right) \tag{11}$$

where  $\gamma$  denotes the portion of the charged voltage. The regeneration energy per cycle  $E_{\text{regen}}$  can be found by subtracting the

10<sup>-1</sup>

را) 10 مار 10 مار

10

10

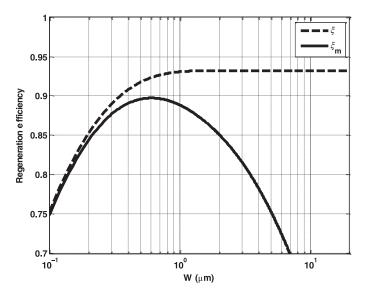

Fig. 12. Regeneration efficiency as a function of the driving transistor width.

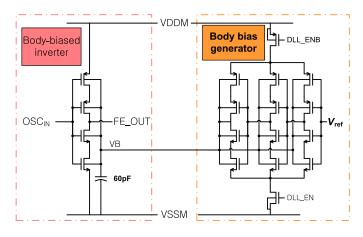

Fig. 13. FE block circuit schematic.

energy pulled from  $C_{eq,sw}$  when SW2 is ON from the energy supplied when SW1 is ON as follows:

$$E_{\text{regen}} = \frac{1}{2} C_{\text{eq,sw}} \left( \left( \frac{V_{\text{DD}} + V_{\text{OSC}} + \Delta V}{2} \right)^2 - \left( \frac{V_{\text{DD}} + V_{\text{OSC}} - \Delta V}{2} \right)^2 \right) - \frac{1}{2} C_{\text{eq,sw}} \left( \left( \frac{V_{\text{DD}} - V_{\text{OSC}} + \Delta V}{2} \right)^2 - \left( \frac{V_{\text{DD}} - V_{\text{OSC}} - \Delta V}{2} \right)^2 \right) = C_{\text{eq,sw}} V_{\text{OSC}} \Delta V = \frac{\gamma}{2 - \gamma} C_{\text{eq,sw}} V_{\text{OSC}} \left( V_{\text{DD}} - V_{\text{OSC}} \right).$$

(12)

Note that when  $\gamma = 1$ ,  $\Delta V = V_{drop}$  and (12) is the same as (8).  $E_{regen}$  is at the maximum of  $C_{eq,sw}V_{OSC}(V_{DD} - V_{OSC})$  in this condition. As the regeneration energy is equal to the lost energy described in (6),  $V_{OSC}$  can be expressed as follows:

$$V_{\rm OSC} = \frac{\left(\frac{\gamma}{2-\gamma}\right) C_{\rm eq,sw}}{\frac{\pi R_m C_{L,\rm TOT}^2}{\sqrt{L_m C_{\rm eq}}} + \left(\frac{\gamma}{2-\gamma}\right) C_{\rm eq,sw}} V_{\rm DD}$$

$$= \frac{\tanh\left(\frac{T_{\rm ON}}{2R_{\rm SW}C_{\rm eq,sw}}\right) C_{\rm eq,sw}}{\frac{\pi R_m C_{L,\rm TOT}^2}{\sqrt{L_m C_{\rm eq}}} + \tanh\left(\frac{T_{\rm ON}}{2R_{\rm SW}C_{\rm eq,sw}}\right) C_{\rm eq,sw}} V_{\rm DD}. \quad (13)$$

Fig. 9 shows the simulated oscillation amplitude as a function of  $\gamma$  compares this to the analytic solution. Since  $\tanh\left(\frac{T_{\rm ON}}{2R_{\rm SW}C_{\rm eq,sw}}\right)$  can be approximated as  $T_{\rm ON}/(2R_{\rm SW}C_{\rm eq,sw})$  when  $T_{\rm ON} \ll R_{\rm SW}C_{\rm eq,sw}$ ,  $V_{\rm OSC}$  can be approximated as follows:

$$V_{\rm OSC} \approx \frac{C_{\rm eq,sw} \frac{T_{\rm ON}}{2R_{\rm sw}C_{\rm eq,sw}}}{\frac{\pi R_m C_{L,\rm TOT}^2}{\sqrt{L_m C_{\rm eq}}}} V_{\rm DD} = \frac{\sqrt{L_m C_{\rm eq}} V_{\rm DD}}{2\pi R_m C_{L,\rm TOT}^2} \cdot \frac{T_{\rm ON}}{R_{\rm sw} C_{\rm eq,sw}}.$$

(14)

Therefore, oscillation amplitude is inversely proportional to the switch resistance when  $R_{SW}$  is large. On the other hand, when  $T_{ON} \gg R_{SW}C_{eq,sw}$ , the switch resistance is small enough to maximize the amplitude, which is noted as the horizontal dotted line in Fig. 9:

$$V_{\text{OSC,max}} = \frac{C_{\text{eq,sw}}}{\frac{\pi R_m C_{L,\text{TOT}}^2}{\sqrt{L_m C_{\text{eq}}}} + C_{\text{eq,sw}}} V_{\text{DD}}.$$

(15)

The discussion to this point shows that the circuit in Fig. 6 differs from a conventional oscillator model where energy is regenerated by a transconductance amplifier. In the conventional model, regenerative current is proportional to oscillation amplitude, making it possible to model the active circuit as a negative resistance. This resistance has to overcome energy loss to maintain oscillation, thus setting a limit on the minimum transconductance the amplifier must provide. However, the oscillation amplitude in (13) shows that the circuit of Fig. 6 can theoretically maintain oscillation with any value of  $T_{\rm ON}$ ,  $R_{SW}$ ,  $C_{eq,sw}$ , as long as  $T_{ON}/(2R_{SW}C_{eq,sw}) > 0$ , which simply means that  $T_{\rm ON}$  is positive. In the proposed circuit, regenerative current provided by switches will increase as oscillation voltage decreases. Therefore, it can eventually reach a steady-state oscillation with no theoretical limit, and cannot be modeled by a negative resistance. However, a practical limit in the proposed design still exists as it must be greater than the minimum oscillation amplitude that can be received as a DLL input with circuit noise present.

Continuing with original discussion, the energy provided by the supply while SW1 is ON can be calculated by multiplying  $V_{\text{DD}}$  with the charge supplied as the following equation:

$$E_{VDD} = \int^{V_{DD}} i_{VDD} (t) dt = V_{DD}Q_{DD}$$

$$= V_{DD}C_{eq,sw}\Delta V = \frac{V_{DD}}{V_{OSC}}E_{regen}.$$

(16)

By combining (12), (14), and (16),  $E_{\text{VDD}}$  can be expressed as the following equation when  $T_{\text{ON}} \ll R_{\text{SW}}C_{\text{eq,sw}}$ :

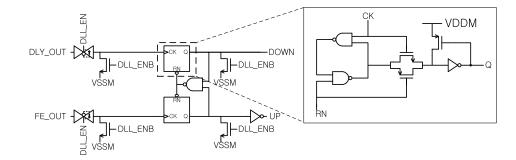

Fig. 14. DLL circuit schematic.

Fig. 15. Edge detector circuit schematic.

$$E_{VDD} = \frac{V_{DD}}{V_{OSC}} E_{\text{regen}} = \frac{V_{DD}}{V_{OSC}} \frac{\gamma C_{\text{eq,sw}} V_{OSC} (V_{DD} - V_{OSC})}{2 - \gamma}$$

$$\approx \tanh\left(\frac{T_{ON}}{2R_{\text{SW}}C_{\text{eq,sw}}}\right) C_{\text{eq,sw}} V_{DD}^{2} \approx \frac{T_{ON} V_{DD}^{2}}{2R_{\text{SW}}}.$$

(17)

It can be seen that a large  $R_{\rm SW}$  reduces the oscillation amplitude and thus, the amount of amplitude that needs to be regenerated  $\Delta V$  is also reduced. On the other hand, when  $R_{\rm SW}$  becomes small, both  $E_{\rm regen}$  and  $V_{\rm OSC}$  approach to their maximum, which can be derived by

$$E_{VDD,max} = \frac{V_{DD}}{V_{OSC,max}} E_{regen,max} = C_{eq,sw} V_{DD} \left( V_{DD} - V_{OSC,max} \right)$$

$$= \frac{\pi R_m C_{L,TOT}^2 C_{eq,sw}}{\pi R_m C_{L,TOT}^2 + C_{eq,sw} \sqrt{L_m C_{eq}}} V_{DD}^2.$$

(18)

Fig. 10 shows simulated and analytic solution of  $E_{VDD}$  according to the switch resistance. Note that  $E_{VDD}$  is inversely proportional to  $R_{SW}$  when  $R_{SW}$  is large while it asymptotically approaches (18) when  $R_{SW}$  is small.

Now that we have computed both the  $E_{\text{VDD}}$  and  $E_{\text{regen}} = E_{\text{loss}}$ , the regeneration efficiency  $\xi$  can be found by taking the ratio between  $E_{\text{regen}}$  and  $E_{\text{VDD}}$  as follows:

- -

$$\xi = \frac{E_{\text{regen}}}{E_{\text{VDD}}} = \frac{V_{\text{OSC}}}{V_{\text{DD}}}$$

$$= \frac{\tanh\left(\frac{T_{\text{ON}}}{2R_{\text{SW}}C_{\text{eq,sw}}}\right)C_{\text{eq,sw}}}{\frac{\pi R_m C_{L,\text{TOT}}^2}{\sqrt{L_m C_{\text{eq}}}} + \tanh\left(\frac{T_{\text{ON}}}{2R_{\text{SW}}C_{\text{eq,sw}}}\right)C_{\text{eq,sw}}}.$$

(19)

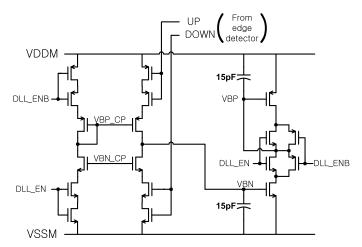

Fig. 16. Charge pump circuit schematic.

From this equation, it is clear that the maximum regeneration efficiency  $\xi_{\text{max}}$  is achieved when  $\gamma$  is equal to 1:

$$\xi_{\max} = \frac{V_{\text{OSC,max}}}{V_{\text{DD}}} = \frac{C_{\text{eq,sw}}}{\frac{\pi R_m C_{L,\text{TOT}}^2}{\sqrt{L_m C_{\text{eq}}}} + C_{\text{eq,sw}}}.$$

(20)

Even though the energy consumption from  $V_{\text{DD}}$  is maximum when  $\gamma = 1$ , most of the energy is delivered to the crystal rather than dissipated in the switches.

However, to achieve this maximum regeneration efficiency, it is necessary that  $R_{\rm SW} \ll T_{\rm ON}/C_{\rm eq,sw}$ . Since  $T_{\rm ON}$  is limited to be a fraction of the oscillation period and  $C_{\rm eq,sw}$  is fixed, maximum efficiency requires  $R_{\rm SW}$  to be reduced. However, the reduction of  $R_{\rm SW}$  requires an increase in the size of the transistors which, in turn, increases the energy consumption for

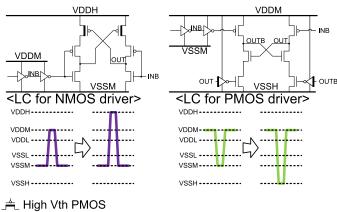

Fig. 17. Level converter circuit schematic.

switching those transistors due to their increased gate capacitance. The switches are in the linear mode when they are turned on and  $R_{SW}$  can be calculated by the following equation:

$$R_{\rm SW} = \frac{L_n}{\mu_n C_{\rm ox} \left( V_{\rm gs} - V_{\rm thn} \right) W_n} = \frac{L_p}{\mu_p C_{\rm ox} \left( V_{\rm sg} - |V_{\rm thp}| \right) W_p}$$

(21)

where  $\mu$ ,  $C_{\text{ox}}$ ,  $V_{\text{th}}$ , W, L, and  $V_{\text{gs}}$  are mobility, unit oxide capacitance, threshold voltage, transistor width, transistor length, and gate-to-source voltage, respectively. The gate capacitance  $C_{\text{sw}}$ is given by  $C_{\text{OX}} \cdot W \cdot L$ . Then, the energy consumed by the switching operation  $E_{\text{SW}}$  can be calculated by the following equation:

$$E_{\rm SW} = (C_{\rm swp} + C_{\rm swn}) V_{\rm sw}^2 \tag{22}$$

where  $V_{\rm SW}$  denotes the gate voltage swing of the transistors. Note that voltage boosting technique is used in this work, so that the  $V_{\rm gs}$  and  $V_{\rm SW}$  are different. More detailed information on the voltage boosting will be explained in Section V. Fig. 11 shows  $E_{\rm VDD}$  and  $E_{\rm SW}$  according to the transistor width when  $R_m =$  $30 \ k\Omega$ ,  $T_{\rm ON} = 200 \ ns$ ,  $L_m = 10.2 \ kH$ ,  $C_m = 2.3129 \ fF$ , and  $C_p = 1.5 \ pF$ ,  $C_{L1} = C_{L2} = 10 \ pF$ ,  $V_{\rm DD} = 180 \ mV$ ,  $\mu = 0.04$ ,  $C_{\rm ox} = 5 \ fF/\mu m^2$ ,  $V_{\rm gs} = 0.63 \ V$  and  $V_{\rm sw} = 0.81 \ V$ . As transistor width increases,  $R_{\rm SW}$  reduces which causes  $E_{V\rm DD}$  to approach  $E_{V\rm DD,max}$  and improves the regeneration efficiency. On the other hand,  $E_{\rm SW}$  is proportional to W as shown in (22), which dissipates additional energy and degrades the overall regeneration efficiency. The modified regeneration efficiency  $\xi_m$ , shown in the following equation, is plotted in Fig. 12:

$$\xi_m = \frac{E_{\text{regen}}}{E_{V\text{DD}} + E_{\text{SW}}}.$$

(23)

Note that there exists an optimal transistor width  $W_{opt}$  that maximizes the regeneration efficiency. In this work, we numerically calculated  $W_{opt} \approx 600$  nm using (12), (13), (16), (21), and (22) and the parameters given above.

Finally, it is worth briefly discussing the optimal duration of  $T_{\rm ON}$  for completeness. Although we assumed above that it is beneficial to maintain  $T_{\rm ON} \gg R_{\rm SW}C_{\rm eq,sw}$ , it is possible to operate the circuit with  $T_{\rm ON} < R_{\rm SW}C_{\rm eq,sw}$ . However, if  $T_{\rm ON}$  is too large, the switch turns on well before the oscillation reaches its peak voltage. This induces a larger current to flow through the switch with a larger voltage across it. Therefore, the efficiency degrades as more energy is dissipated through the switches. The simulation result shows efficiency degradation as  $T_{\rm ON}$  becomes larger than 3 µs, representing roughly 10% of the oscillation period.

#### V. IMPLEMENTATION DETAIL

In this section, the details of each block will be discussed. Most of the circuit operates from the medium-voltage supply, which includes the FE, DLL, and PG, and which forms the core of the system. After these circuit elements, the level converter and SCN will be explained.

Fig. 13 shows the FE block. Since the crystal oscillates as a sine wave within the low-voltage supply, the sine wave needs to be converted to square wave within medium-voltage supply for the DLL to work. Since the FE operates at a near-threshold voltage level, where the circuit is more prone to PVT variation, a simple inverter may not be able to generate a 50% duty-cycle square wave if either NMOS or PMOS is stronger than the other. However, the FE output needs to trip exactly in the middle of low-voltage supply, even with PVT variation. Therefore, a self-adaptive body-biasing technique is used for the FE [12]. The body-biased inverter will amplify the sine wave from the crystal while a separate body bias generator dynamically adjusts the body bias, so that trip voltage is set as required. However, the body-biased generator itself consumes more than a few nW of power if it runs continuously. Therefore, the body-biased voltage is held on an on-chip 60 pF capacitor and adjusted only twice every 32 cycles. If needed, the circuit configuration can be changed to recalibrate this value for 2 out of 32 cycles, 4 out of 32 cycles, 2 out of 16 cycles, or constantly. The test result in the next section was measured with fixed setting at 2 out of 32 cycles for all testing environments of voltage and temperature. The reference voltage is equal to midrail voltage of a medium-voltage supply pair, and it is generated on-chip using a stack of diode-connected transistors operating at low pW range. Additionally, a double-stacked inverter topology is used throughout the circuit, which helps to reduce power consumption by 46% for the FE block.

Fig. 14 shows the DLL block. Delay cells are made with current-starved inverters, double stacked to minimize any leakage. Then, a pair of outputs from the DLL is chosen by the multiplexer for the pulse generator (PG). Depending on which cells are chosen, the PG can be reconfigured to use appropriate logic gates, so that correct pulses can be sent to the drivers. The test chip in the next section was implemented without a closed-loop pulse controller. Therefore, it was tested with a fixed pulse setting having enough margin to enable reliable operation across all testing conditions. Fig. 15 shows the edge detector of the DLL. Instead of using a standard flip-flop (FF), custom cells have been designed to reduce the number of transistors from 36 in a standard cell FF to 13. Simulation results show that FF power is reduced by 55%. Similar to the bodybiased generator in the FE, the edge detector will only operate periodically. This may cause concern about worse frequency

Fig. 18. SCN block diagram.

Fig. 19. Detail of SCN for voltage generation. A and B refer to nonoverlapping clock pair. Dotted line represents decoupling capacitor.

stability. However, as it will be explained in the next section, the long-term stability does not show noticeable impact, due to innate frequency stability performance of the quartz crystal.

Fig. 16 shows the charge pump of the DLL. Similar to other parts shown previously, double stacking is used when needed, and the circuit operates periodically while relying on large capacitors to hold the bias voltage. Although not shown in the figure for simplicity, the bias voltage for the charge pump is also internally generated and it is assisted by on-chip capacitors.

Overall, when DLL and FE need to recalibrate their bias voltage, all the circuit parts previously explained will be activated. Measurement result confirmed that the circuit can sustain oscillation while running in this mode for only 2 out of every 32 cycles. Then, for the remaining 30 cycles, only blocks in the main signal path (FE, delay cells, and PG) operate to save power. The DLL\_EN signal in Figs. 13, 15, and 16 is driven low for 30 cycles to minimize switching activity and store analog voltage on dedicated capacitors. Careful connection is required to retain analog voltage levels such as those of the cut-off transistors of the current mirror in Fig. 16. If the VBP node is connected directly to the drain of the PMOS transistor, its

voltage will leak when DLL\_EN is low. In order to prevent this, additional cut-off transistors are added in between the drain and VBP node, so that it works as an ordinary current mirror for two cycles and then retains its voltage for 30 cycles.

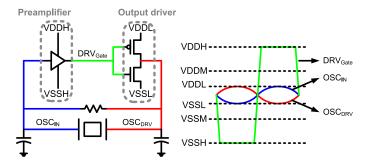

Fig. 17 shows the level converter. The pulse generated from previous blocks is still in the medium-voltage supply. In order to have the low ON-resistance (i.e.,  $R_{SW}$ ), the pulse needs to be up-converted to the high-voltage supply level. Since the two pulses are sent to different types of transistors, the upconversion requirement is different for each. For example, when the pulse for the NMOS driver is converted to high voltage, the maximum voltage is increased to  $V_{\text{DDH}}$ , whereas the minimum voltage level does not need to be changed since it is already lower than  $V_{SSL}$ . Similarly, the minimum voltage needs to be decreased to  $V_{\rm SSH}$  for the PMOS pulse. To build a robust level converter with PVT variation tolerance, a new level converter is designed to reduce the contention between pull-up and pull-down path during transition. For the PMOS driver, a high-threshold voltage inverter acting as a delay element is inserted in the circuit to completely turn OFF the contention path during switching for more robust transition [13]. Once the level

10 8 Frequency change (ppm) 6 4 2 0 - Early Normal -2 Late Full \_4 0.95 1.00 1.05 1.10 1.15 1.20 0.90  $V_{\rm DD}$  (V)

Fig. 23. Measurement of normalized frequency at different pulse location.

Fig. 20. Die photograph of the circuit.

Fig. 21. Measured waveform.

Fig. 22. Power at different power supply voltage.

conversion is done, this signal is applied to the gate terminal of output driver transistors.

As explained earlier, the circuit has its own SCN to generate the different voltage pairs required for each of the circuit

Fig. 24. Frequency at different temperature.

Fig. 25. Allan deviation measurement and comparison to prior ultra-low-power RTC.

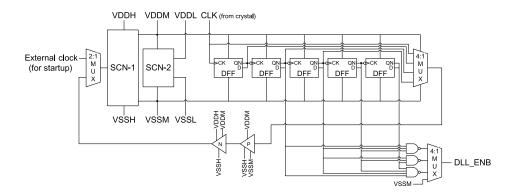

blocks. A key constraint is performing this voltage generation without the conversion dominating the power consumption (i.e., maintaining high-conversion efficiency). Considering parasitic capacitance from switching components, higher SCN efficiency is obtained using a larger switching capacitor that operates at a lower frequency, with the crystal's excellent frequency stability minimizing the effect from higher ripple in supply voltage. The SCN is operated using a 4.096 kHz signal, generated by dividing the crystal frequency by  $8 \times$  and level-converting to high-voltage supply level, as shown in Fig. 18. SCN-1 generates the medium-voltage supply pair from the high-voltage supply pair. Then, SCN-2 uses the medium-voltage supply to generate the low-voltage supply pair. SCN-1 and SCN-2 are designed to be reconfigurable to provide six different division ratios as shown in Fig. 19. Each capacitor is sized at 36 pF, and all supply-voltage nodes are decoupled by 100 pF capacitors. All the testing results in the following section were obtained using an SCN-1 division ratio of 2:1 (SCN-1 Conf. B) and an SCN-2 division ratio of 3:1 (SCN-2 Conf. B). The SCN consumes 0.463 nW in this configuration operating from 4.096 kHz clock signal. It requires 3.04 nW when operated from 32.768 kHz clock signal. The SCN is responsible for 80% of the chip area in the test chip introduced in the next section. This area could be reduced with slight reduction in power efficiency and using a fixed conversion ratio. This overhead can further be reduced if this circuit is implemented as part of a battery-operated sensor node system such as [4], where some voltage levels are readily available with the system's own SCN. Before the crystal starts to oscillate, the SCN requires a separate clock source during start-up to establish the needed output voltage levels. Although not implemented in the test chip, a simple ring oscillator can be used as a start-up clock to perform this task, after which it could be power gated with negligible leakage.

A triple well was used in the circuit implementation. Since the  $V_{SS}$  voltage for certain parts of the circuit is above the substrate ground level, these circuits will have negative body bias without the use of a triple well. This increases the threshold voltage of the transistors and makes it necessary to use a larger supply voltage for stable operation, resulting in increased power consumption. Hence, a triple well was used for all circuits which had a virtual ground higher than the substrate voltage to avoid unintentional biasing of the body nodes.

For the crystal to start the oscillation, the conventional inverter-based circuit is implemented in parallel to the proposed circuit. At the same time, SCN requires a separate clock signal during the start-up sequence since its clock signal during normal operation is generated from the circuit operating from the voltage generated by SCN. For this implementation, an external clock signal was provided for ease of testing. Once SCN output voltage is established and the crystal starts to oscillate using the conventional inverter based circuit, SCN clock signal is internally generated from the clock dividers. At this point, both the conventional start-up circuit and external clock signal can be safely removed and the proposed circuit can maintain the oscillation. The external clock signal can potentially be replaced by using a clock signal multiplexer and using the conventional inverter circuit's output during start-up.

## VI. MEASUREMENT RESULT

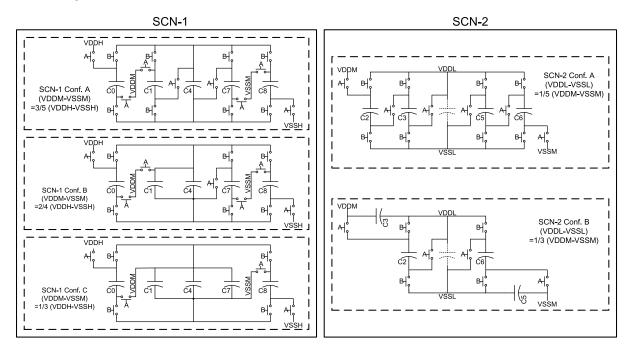

The proposed circuit was fabricated in 0.18  $\mu$ m CMOS technology with a triple well. Fig. 20 shows the die photograph of

TABLE I Performance Summary

| Minimum power consumption                  | 5.58 nW                |

|--------------------------------------------|------------------------|

| Operating temperature tested               | -20°C to 80°C          |

| Frequency drift within testing temperature | -4.56 ppm to 133.3 ppm |

| Supply voltage dependence                  | 30.3 ppm/V             |

| Allan deviation at 1000 s averaging window | $1.16 \times 10^{-8}$  |

the implemented circuit. The total area is 0.3 mm. The chip was wire-bonded on a ceramic PGA package of size 37 mm  $\times$  37 mm. The chip was mounted on PCB and connected to crystal and explicit 5 pF capacitors at each node of the crystal. Authors expect the load capacitance to be in range 10–20 pF with this measurement setup. Fig. 21 shows the measured waveform and displays the pulsing scheme at each oscillation cycle. The OSC<sub>IN</sub> and OSC<sub>OUT</sub> voltage waveforms deviate very slightly from an ideal sinusoid due to the current injection of the output driver. As a result, these nodes voltages contain harmonics which could have impact on the jitter performance of the circuit. Based on the measured Alan deviation, this impact appears to be small or negligible although further study of this issue is needed.

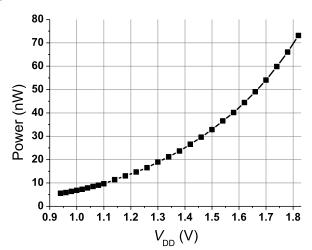

The power consumption of the complete circuit, including on-chip voltage generation by the SCN, at different input power supply voltages  $(V_{\text{DDH}})$  is shown in Fig. 22. As expected, the curve shows a quadratic dependence on voltage and a minimum power of 5.58 nW was observed at room temperature. At this point, SCN is configured to generate  $V_{\text{DDM}}$  –  $V_{\text{SSM}} = 0.47 \text{ V}$  and  $V_{\text{DDL}} - V_{\text{SSL}} = 0.16 \text{ V}$ . For the remainder of the test result such as the temperature sweep, an input supply voltage of  $V_{\text{DDH}} = 1.08 \text{ V}$  was used, which had a power consumption of 9.05 nW and  $V_{\rm DDM} - V_{\rm SSM} = 0.54 \ {\rm V}$  and  $V_{\text{DDL}} - V_{\text{SSL}} = 0.18 \text{ V}$  when not loaded. All supply voltage pairs are centered at half the voltage of  $V_{\text{DDH}}$ , giving  $V_{\text{DDM}} =$ 0.81 V,  $V_{\rm DDL}=0.63$  V,  $V_{\rm SSL}=0.45$  V, and  $V_{\rm SSM}=0.27$  V if unloaded. Measured frequency at this setup was 32767.83 Hz at 25 °C. This frequency is slower by 5.07 ppm from ideal frequency of 32768 Hz, but still within the normal process variation of the crystal.

The experimental results in Fig. 23 show the frequency change under different supply voltage variation and pulse location. Normal in Fig. 23 means the pulse was generated centered at the oscillation minima and maxima, as shown in the measured waverforms in Fig. 21. Early is the case when the pulses were generated before the oscillation peak, and late is the case when the pulses were generated after the oscillation peak. Full means the pulses were generated while centered at the oscillation peaks with a three times wider pulse width. The graph shows frequency change normalized to frequency with normal pulse at supply voltage of 1 V. The circuit shows 30.3 ppm/V over 0.94-1.2 V. Within 10% of the supply voltage at 1.08 V, the frequency drift is approximately 7 ppm, which is small compared to the innate temperature variation of the crystal from -20 °C to 80 °C. In comparison, the conventional circuit which has only one inverter and power consumption in µW range is 1.89 ppm/V. Fig. 23 shows that pulse location and width affect oscillation frequency by only a

|                                   | [9]                                       | [18]    | [6]                     | [17]               | [19]                 | [14]                                | This work             |

|-----------------------------------|-------------------------------------------|---------|-------------------------|--------------------|----------------------|-------------------------------------|-----------------------|

| Technology                        | 2 µm                                      | 2 µm    | 130 nm                  | 130 nm             | 65 nm                | 28 nm                               | 180 nm                |

| Area<br>(mm <sup>2</sup> )        | N/A                                       | N/A     | 0.015                   | 0.019              | 0.015                | 0.0028                              | 0.3                   |

| Original<br>work<br>published     | 1999                                      | 1994    | 2012                    | 2009               | 2014                 | 2014                                | 2012                  |

| Architecture                      | Amplitude-regulated<br>crystal oscillator |         | CMOS-based timer        |                    |                      | Pulsed driver<br>crystal oscillator |                       |

| Frequency<br>(kHz)                | 32.768                                    | 32.768  | 3.7–14 Hz               | 11 Hz              | 32.768               | 32.768                              | 32.768                |

| Reported<br>supply<br>voltage (V) | 0.71-2.6                                  | 1.1–2.2 | 0.65–0.75,<br>1.15–1.25 | 0.55-0.6           | 1.15-1.45            | 0.15-0.5                            | 0.94-1.82             |

| Tested<br>temperature<br>(°C)     | N/A                                       | 0 to 50 | -20 to 80               | 0 to 90            | -20 to 90            | -20 to 80                           | -20 to 80             |

| Power<br>consumption<br>(nW)      | 27                                        | 220     | 0.66                    | 0.15               | 190                  | 1.89                                | 5.58<br>(with<br>SCN) |

| Allan<br>deviation<br>floor       | N/A                                       | N/A     | < 5×10 <sup>-5</sup>    | < 10 <sup>-4</sup> | < 4×10 <sup>-6</sup> | < 10 <sup>-8</sup>                  | ~ 10 <sup>-8</sup>    |

TABLE II Comparison to Other Works

few ppm. This shows that the circuit can maintain acceptable frequency performance even if DLL performance degrades. This suggests that possible simplifications can be made to the pulse generation: trading off accuracy of the pulse position for reduced power consumption as has been exploited successfully in a more recent work [14] using a similar approach to this work [15].

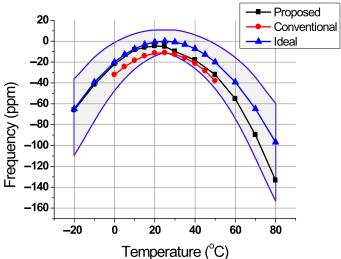

Fig. 24 shows the frequency dependence on temperature. The innate frequency characteristic of the crystal itself is shown in the blue line, as specified by the crystal's datasheet [16]. The shaded region marks the specification boundary due to process variation of the crystal itself. The solid black line shows the result of the proposed circuit. The graph shows that the circuit remains well within the specification boundary. Shown in the red line is the conventional circuit result.

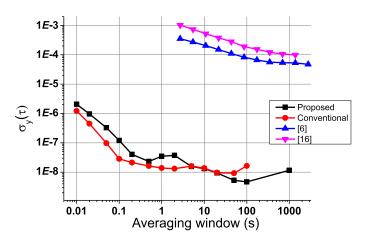

To use this circuit as a real-time clock in wireless sensor node, long-term frequency stability is of the utmost importance. Shown in Fig. 25 is the Allan deviation of the proposed circuit and the conventional inverter-based XO circuit. The red line shows the measurement result of the proposed circuit, and the black line is the measured result of the conventional inverter-based crystal oscillator operating at 32.768 kHz. The proposed circuit experiences Allan deviation of approximately  $10^{-8}$  over a 1000 s time window. This translates into 36 µs of random error in an hour, which causes an average overhead of 10 pW due to timer mismatch in the scenario discussed in Section I and shown in Fig. 1. The result shows that the circuit maintains stability performance needed for a WSN. For comparison, Allan deviation measurement results for ultra-low-power silicon-based timers are shown [6], [17]. They have approximately one order of magnitude lower power consumption (0.15 nW for [17] and 0.66 nW for [6]) as the proposed circuit (5.58 nW) but four orders of magnitude worse frequency stability performance than the proposed circuit.

Tables I and II show the performance summary, along with comparison to other crystal oscillator works [9], [14], [18] and low-power CMOS-based timers [6], [17], [19]. The proposed circuit achieves  $4.84 \times$  lower minimum power than [9]. The power includes on-chip SCN and divided clock signal generation at full-supply voltage level.

#### VII. CONCLUSION

A new XO architecture was proposed which uses low-voltage supply to keep small oscillation amplitude and high-voltage supply for strong drivers. To the authors' best knowledge, this work is the first to use pulsed input to the driver to sustain the oscillation of the quartz crystal. Together with the pulse injection scheme realized by DLL, the power could be reduced to 5.58 nW, which is  $4.84 \times$  lower than the previous work. It shows a wide-operating supply voltage of 0.94-1.82 V with supply voltage dependence of 30.3 ppm over 0.94-1.2 V. Frequency measurement from -20 °C to 80 °C shows that the circuit does not degrade the excellent frequency performance of the quartz crystal. The long-term frequency stability performance is confirmed by Allan deviation of  $1.16 \times 10^{-8}$  and meets the requirement for WSN application.

## REFERENCES

- G. Bell, "Bell's law for the birth and death of computer classes: A theory of the computer's evolution," *IEEE Solid-State Circuits Soc. Newslett.*, vol. 13, no. 4, pp. 8–19, Feb. 2008.

- [2] J. M. Kahn, R. H. Katz, and K. S. J. Pister, "Next century challenges: Mobile networking for 'smart dust'," in *Proc. 5th Annu. ACM/IEEE Int. Conf. Mobile Comput. Netw.*, 1999, pp. 271–278.

- [3] E. Chow, S. Chakraborty, W. Chappell, and P. Irazoqui, "Mixed-signal integrated circuits for self-contained sub-cubic millimeter biomedical implants," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers* (*ISSCC*), Feb. 2010, pp. 236–237.

- [4] Y. Lee *et al.*, "A modular 1 mm<sup>3</sup> die-stacked sensing platform with low power I<sup>2</sup>C inter-die communication and multi-modal energy harvesting," *IEEE J. Solid-State Circuits*, vol. 48, no. 1, pp. 229–243, Jan. 2013.

- [5] W. Lim, I. Lee, D. Sylvester, and D. Blaauw, "Batteryless sub-nW cortex-M0+ processor with dynamic leakage-suppression logic," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers (ISSCC)*, Feb. 2015, pp. 146– 147.

- [6] Y. Lee, B. Giridhar, Z. Foo, D. Sylvester, and D. Blaauw, "A 660 pw multi-stage temperature-compensated timer for ultra-low-power wireless sensor node synchronization," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers (ISSCC)*, Feb. 2011, pp. 46–48.

- [7] E. Vittoz and J. Fellrath, "CMOS analog integrated circuits based on weak inversion operations," *IEEE J. Solid-State Circuits*, vol. SC-12, no. 3, pp. 224–231, Jun. 1977.

- [8] E. Vittoz, M. Degrauwe, and S. Bitz, "High-performance crystal oscillator circuits: Theory and application," *IEEE J. Solid-State Circuits*, vol. SC-23, no. 3, pp. 774–783, Jun. 1988.

- [9] W. Thommen, "An improved low power crystal oscillator," in *Proc. 25th Eur. Solid-State Circuits Conf. (ESSCIRC)*, Sep. 1999, pp. 146–149.

- [10] S. Oh, N. Roberts, and D. Wentzloff, "A 116 nW multi-band wake-up receiver with 31-bit correlator and interference rejection," in *Proc. IEEE Custom Integr. Circuits Conf.*, Sep. 2013, pp. 1–4.

- [11] G. Chen et al., "A cubic-millimeter energy-autonomous wireless intraocular pressure monitor," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers (ISSCC)*, Feb. 2011, pp. 310–312.

- [12] S. Chatterjee, Y. Tsividis, and P. Kinget, "0.5-V analog circuit techniques and their application in OTA and filter design," *IEEE J. Solid-State Circuits*, vol. 40, no. 12, pp. 2373–2387, Dec. 2005.

[13] Y. Kim, D. Sylvester, and D. Blaauw, "LC<sup>2</sup>: Limited contention level

- [13] Y. Kim, D. Sylvester, and D. Blaauw, "LC<sup>2</sup>: Limited contention level converter for robust wide-range voltage conversion," in *IEEE Symp. VLSI Circuits Dig. Tech. Papers*, Jun. 2011, pp. 188–189.

- [14] K.-J. Hsiao, "A 1.89 nW/0.15 V self-charged XO for real-time clock generation," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers* (*ISSCC*), Feb. 2014, pp. 298–299.

- [15] D. Yoon, D. Sylvester, and D. Blaauw, "A 5.58 nW 32.768 kHz DLLassisted XO for real-time clocks in wireless sensing applications," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers (ISSCC)*, Feb. 2012, pp. 366–368.

- [16] ECS, Inc. International, ECS-2X6-FLX SMD Tuning Fork Crystal [Online]. Available: http://www.ecsxtal.com/store/pdf/ecs-2x6-flxr.pdf

- [17] Y. S. Lin, D. Sylvester, and D. Blaauw, "A 150 pW program-and-hold timer for ultra-low-power sensor platforms," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers (ISSCC)*, Feb. 2009, pp. 326–327.

- [18] D. Lanfranchi, E. Dijkstra, and D. Aebischer, "A microprocessor-based analog wristwatch chip with 3 seconds/year accuracy," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers (ISSCC)*, Feb. 1994, pp. 92–93.

- [19] D. Griffith, P. T. Roine, J. Murdock, and R. Smith, "A 190 nW 33 kHz RC oscillator with ±0.21% temperature stability and 4 ppm long-term stability," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, Feb. 2014, pp. 300–301.

**Dongmin Yoon** (S'10–M'15) received the B.S. degree in electrical engineering from Seoul National University, Seoul, South Korea, in 2009, and the M.S. and Ph.D. degrees in electrical engineering from the University of Michigan, Ann Arbor, MI, USA, in 2011 and 2015, respectively.

In 2015, he joined the Communication and Devices Group, Intel Corporations, Hillsboro, OR, USA, where he is currently an Analog Engineer.

**Taekwang Jang** received the B.S. and M.S. degrees in electrical engineering from KAIST, Daejeon, South Korea, in 2006 and 2008, respectively. He is currently working toward the Ph.D. degree at the University of Michigan, Ann Arbor, MI, USA.

In 2008, he joined Samsung Electronics Company Ltd., Giheung, South Korea. His research interests include system clock generation, data converters, and ultra-low power sensor node design.

**Dennis Sylvester** (S'95–M'00–SM'04–F'11) received the Ph.D. degree in electrical engineering from the University of California, Berkeley, CA, USA, where his dissertation was recognized with the David J. Sakrison Memorial Prize as the most outstanding research in the UC-Berkeley EECS Department.

Ĥe is a Professor of Electrical Engineering and Computer Science with the University of Michigan, Ann Arbor, MI, USA, and the Director of the Michigan Integrated Circuits Laboratory (MICL), a

group of 10 faculty and more than 70 graduate students. He has held Research Staff positions with the Advanced Technology Group of Synopsys, Mountain View, CA, USA, Hewlett-Packard Laboratories, Palo Alto, CA, USA, and Visiting Professorships at the National University of Singapore, Singapore, and Nanyang Technological University, Singapore. He is the co-founder of Ambiq Micro, Austin, TX, USA. He has authored or coauthored over 400 articles along with one book and several book chapters. He holds 26 US patents. His research interests include the design of millimeter-scale computing systems and energy-efficient near-threshold computing.

Dr. Sylvester serves on the Technical Program Committee of the IEEE International Solid-State Circuits Conference and previously served on the Executive Committee of the ACM/IEEE Design Automation Conference. He has served as Associate Editor for the IEEE TRANSACTIONS ON CAD and the IEEE TRANSACTIONS ON VLSI SYSTEMS and as Guest Editor for the IEEE TRANSACTIONS ON VLSI SYSTEMS and as Guest Editor for the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS II. He also serves as a Consultant and Technical Advisory Board Member for electronic design automation and semiconductor firms. He was the recipient of the NSF CAREER Award, the Beatrice Winner Award at ISSCC, an IBM Faculty Award, an SRC Inventor Recognition Award, nine Best Paper Awards and nominations, the ACM SIGDA Outstanding New Faculty Award, and the University of Michigan Henry Russel Award for distinguished scholarship.

**David Blaauw** (M'09–F'12) received the B.S. degree in physics and computer science from Duke University, Durham, NC, USA, in 1986, and the Ph.D. degree in computer science from the University of Illinois at Urbana-Champaign, Champaign, IL, USA, in 1991.

He worked with Motorola Inc., Austin, TX, USA, where he was the Manager of the High Performance Design Technology Group. Since August 2001, he has been on the Faculty at the University of Michigan, Ann Arbor, MI, USA, where he is a Professor. He

has authored or coauthored over 450 papers and holds 40 patents. His research interests include VLSI design with particular emphasis on ultra-low power and high-performance design.

Dr. Blaauw was the Technical Program Chair and General Chair for the International Symposium on Low Power Electronic and Design. He was also the Technical Program Co-Chair of the ACM/IEEE Design Automation Conference and a member of the ISSCC Technical Program Committee.