# A 120nW 8b Sub-ranging SAR ADC with Signal-Dependent Charge Recycling for **Biomedical Applications**

Seokhyeon Jeong<sup>1</sup>, Wanyeong Jung<sup>1</sup>, Dongsuk Jeon<sup>2</sup>, Omer Berenfeld<sup>3</sup>, Hakan Oral<sup>3</sup>, Grant Kruger<sup>3</sup>, David Blaauw<sup>1</sup>, Dennis Sylvester<sup>1</sup> University of Michigan, Ann Arbor, MI, <sup>2</sup>Massachusetts Institute of Technology, Cambridge, MA, <sup>3</sup>University of Michigan Health System, Ann Arbor, MI

#### **Abstract**

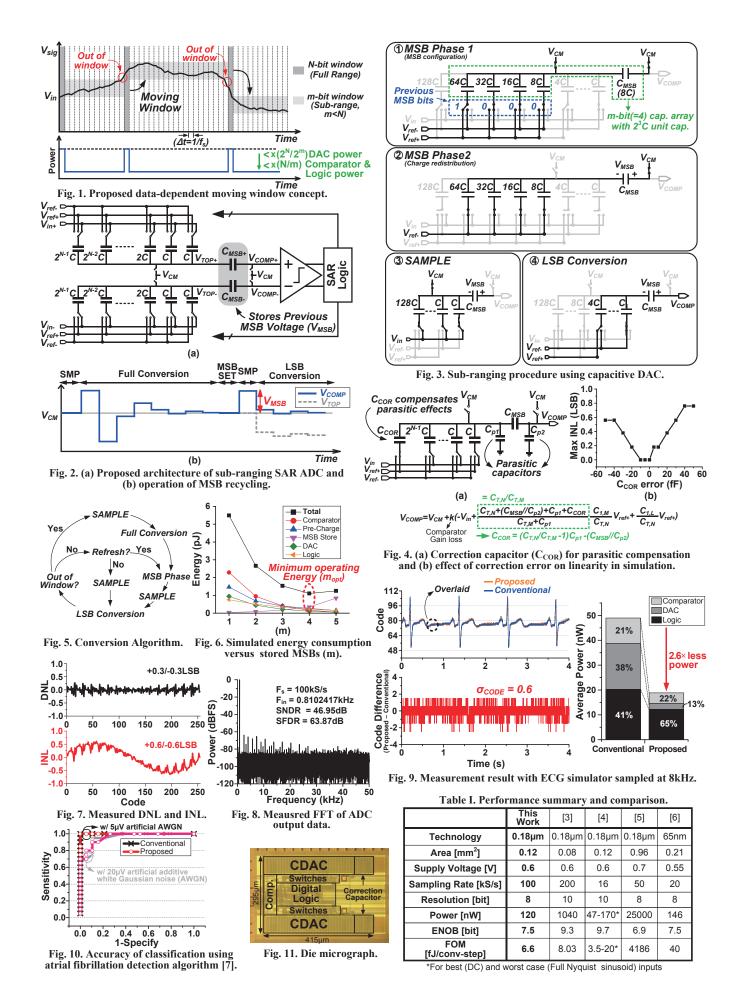

We present an 8-bit sub-ranging SAR ADC designed for bursty signals having long time periods with small code spread. A modified capacitive-DAC (CDAC) saves previous sample's MSB voltage and reuses it throughout subsequent conversions. This prevents unnecessary switching of large MSB capacitors as well as conversion cycles, reducing energy consumed in the comparator and digital logic and yielding total energy savings of 2.6×. In 0.18µm CMOS, the ADC consumes 120nW at 0.6V and 100kS/s with 46.9dB SNDR.

### Introduction

Interest in wireless sensor networks has grown recently for biomedical (ExG) and environmental monitoring (e.g., temperature and pressure) applications [1-2]. In these sensor interfaces, the SAR ADC is a common choice due to low power consumption and high energy efficiency. Many signals in these targeted application areas have the following characteristics: 1) Low activity for the majority of the time, i.e., short-term signal variation is small; 2) Long-term signal variation is wide; and 3) Bursts of activity occasionally occur within a short time period, such as a neuron spike. Several recent works were proposed that take advantage of these signal characteristics. A bypass window technique [3] skips bit cycles when the signal is within a predefined range while an LSB-first approximation [4] starts the conversion from the previous sample. Another approach [5] modulates sampling rate according to signal activity. However, a predefined window cannot track a signal's low activity region while the LSB-first approximation toggles MSBs in the DAC every cycle for an initial guess, consuming energy. In this work, we propose a sub-ranging ADC that uses a moving window and stores the previous MSBs voltage value on a series capacitor. This enables the MSBs of the CDAC to be held fixed in subsequent cycles. Due to the large MSB capacitors size, substantial energy is saved in the CDAC as well as the comparator and logic. Energy savings are signal dependent; the approach was applied to 39 actual ECG recordings and showed 2.6× energy savings while fully preserving arrhythmia detection accuracy.

#### **Proposed Circuit**

Fig. 1 describes the conceptual operation of the proposed N-bit ADC. After an initial full conversion, an *m*-bit sub-ranging window is set based on the conversion result. Then, the next conversion begins within that window, skipping conversion cycles for m MSBs. The architecture is similar to the conventional SAR ADC except for a series capacitor (C<sub>MSB</sub>) between CDAC and comparator (Fig. 2a). C<sub>MSB</sub> is used to store the voltage corresponding to the most significant m-bits ( $V_{MSB}$ ) from the previous sample (Fig. 2b). If the next sample falls within the same sub-ranging window, energy to switch the MSB capacitors reduces dramatically (by  $16\times$  for 4 MSBs in an 8-bit SAR) while comparator and logic energy reduces linearly with the number of MSBs stored due to reduced conversion cycles. When the signal goes out of the predefined window, the ADC switches back to full-range mode for one cycle to re-acquire the signal.

Fig. 3 shows detailed ADC operation. In MSB phase 1, the selected m-bit capacitor array is configured based on the previous MSBs. In phase 2, selected capacitors are connected to V<sub>ref</sub> for charge redistribution. As a result, the m-bit MSB voltage of the previous sample is stored across C<sub>MSB</sub>. Unselected capacitors in the CDAC are precharged to (V<sub>ref+</sub>-V<sub>CM</sub>) during MSB phase 1 to prevent the bottom plate voltage from going below ground due to capacitive coupling in MSB phase 2. After the C<sub>MSB</sub> is set, the subsequent sample and conversion phases are the same as in conventional SAR operation except that only LSBs are computed. During LSB conversion V<sub>COMP</sub> can be expressed as:

$$\begin{aligned} \mathbf{V}_{COMP} &= V_{CM} + -V_{in} + (\frac{C_{1,M}}{C_{T,M}} + \frac{C_{1,L}}{C_{T,N}})(V_{ref+} - V_{ref-}), \\ \text{where } C_{T,M} \text{ is the capacitance of } m\text{-bit capacitor array, } C_{T,N} \text{ is the} \end{aligned}$$

capacitance of the N-bit capacitor array,  $C_{I,M}$  and  $C_{I,L}$  are the sum of all capacitances connected to V<sub>ref+</sub> during MSB phase 1 and LSB conversion, respectively. This conversion process is identical to the conventional SAR approach. Since total charge at node V<sub>COMP</sub> remains constant, the voltage across C<sub>MSB</sub> always returns to V<sub>MSB</sub> at the end of conversion, enabling reuse of the MSB information.

Due to parasitic capacitances, the stored charge will not be scaled correctly during LSB conversions, which causes non-uniformity between sub-ranging windows. This is solved by introducing a correction capacitor (C<sub>COR</sub>, Fig. 4a). C<sub>COR</sub> is connected to V<sub>ref</sub> during LSB conversions to cancel out this scaling error and is connected to V<sub>ref+</sub> in MSB phase 1 for pre-charging. When C<sub>COR</sub> is correctly set, the conversion process becomes immune to parasitic capacitances. Simulated INL across C<sub>COR</sub> error shows that linearity is relatively insensitive to the absolute value of C<sub>COR</sub> (Fig. 4b).

As leakage on  $C_{\mbox{\scriptsize MSB}}$  can cause errors as time passes, a refresh rate is set to restore V<sub>MSB</sub> (0 to 63 cycles in our implementation). This rate can be optimized to maximize energy savings depending on the environment (e.g., temperature). When the conversion result is out of the sub-range, an error flag is set and C<sub>MSB</sub> is reset in the subsequent full-range conversion. Fig. 5 shows the overall operating algorithm.

Total energy consumed by the proposed ADC depends on the number of MSBs (m) that are stored on  $C_{MSB}$  for sub-ranging (Fig. 6). As m increases, pre-charge energy for the unused capacitors goes down as well as comparator, DAC, and logic energy due to fewer cycles for conversion. However, energy and frequency of storing the MSB voltage increases. Simulation showed a minimum operating energy when m is 4 bits. Note that energy is consumed for storing MSB and pre-charging only when the signal is out of the sub-ranging window (3.7% of total cycle during ECG detection). The selection of the unit capacitance in the *m*-bit capacitor array also impacts energy. A lower capacitance is preferred to reduce energy during MSB configuration, but comparator energy increases due to the need to compensate for gain loss arising from the series connection of C<sub>MSB</sub> and C<sub>p2</sub>. The ADC uses a StrongARM comparator with 3-sigma offset of ±30mV, calibrated with binary 4-bit capacitors at the comparator outputs. CDAC is composed of 4.5fF MOM unit capacitors.

## Measurements

The test chip is fabricated in 0.18µm CMOS with an area of 0.12mm<sup>2</sup>. The proposed design is tested at 100kS/s and operates from a single 0.6V supply voltage. Measured DNL and INL are +0.3/-0.3 LSB and +0.6/-0.6 LSB, respectively (Fig 7). Fig. 8 shows the measured power spectrum. Measured SNDR and SFDR are 46.9dB and 63.8dB, respectively. Fig. 9 shows measured data from an ECG simulator. Power reduces by 2.6× compared to an 8-bit conventional SAR ADC with negligible data loss. Effectiveness of the sub-ranging approach is assessed with an atrial fibrillation detection algorithm [7] using 39 actual patient ECG waveforms (Fig. 10). Fig. 10 shows that the classifier output is identical with the conventional and proposed ADCs, indicating the potential of this approach for biomedical applications. Fig. 11 shows the chip micrograph. Table I summarizes this work and compares against state-of-art SAR ADCs with similar application focus.

## References

- [2] Y.-J Huang et al., VLSI, 2013. [1] D. Jeon et al., ISSCC, 2014. [3] G.-Y Huang et al., JSSC, Nov. 2012. [4] F. M. Yaul et al., ISSCC, 2014.

- [5] M. Trakimas et al., TCAS, 2011. [6] M. Yip et al., ISSCC, 2011.

- [7] H. Oral et al., U.S. Patent 201 3019 7380 A1, Aug. 2013.