## 23.3 A 3nW Fully Integrated Energy Harvester Based on Self-Oscillating Switched-Capacitor DC-DC Converter

Wanyeong Jung, Sechang Oh, Suyoung Bang, Yoonmyung Lee, Dennis Sylvester, David Blaauw

University of Michigan, Ann Arbor, MI

Recent advances in low-power circuits have enabled mm-scale wireless systems [1] for wireless sensor networks and implantable devices, among other applications. Energy harvesting is an attractive way to power such systems due to limited energy capacity of batteries at these form factors. However, the same size limitation restricts the amount of harvested power, which can be as low as 10s of nW for mm-scale photovoltaic cells in indoor conditions. Efficient DC-DC up-conversion at such low power levels (for battery charging) is extremely challenging and has not yet been demonstrated.

Boost DC-DC converters are widely used to harvest energy from DC sources and yield high conversion efficiency [2]. However, they require a large off-chip inductor at low harvested power levels, increasing system size. Alternatively, switched-capacitor (SC) DC-DC converters can be fully integrated on-chip and are favored for form-factor constrained applications [3-8]. However, at low power levels, SC converter efficiency has been constrained by overheads of clock generation and level-conversion to drive the switch capacitors. As a result, efficient SC converter operation has been limited to the  $\mu W$  range.

This paper presents a fully integrated energy harvester maintaining >35% end-to-end efficiency when harvesting from a  $0.84 mm^2$  solar cell in low light condition of 260lux, converting 7nW input power from 250mV to 4V. The key contribution of this work lies in the proposed SC DC-DC voltage doubler structure, in which an oscillator is completely internalized within the SC network. This eliminates power overhead of clock generation and level shifting, and enables higher efficiency at lower power levels. Voltage doublers are cascaded to form a complete harvester with a wide load range from 5nW to 5 $\mu$ W and self-starting operation down to 140mV. Since each doubler is self-oscillating, the frequency of each stage can be independently modulated, thereby optimizing the overall conversion efficiency. The harvester conversion ratio is configurable from  $9\times$  to  $23\times$  and idle power consumption is less than 3nW.

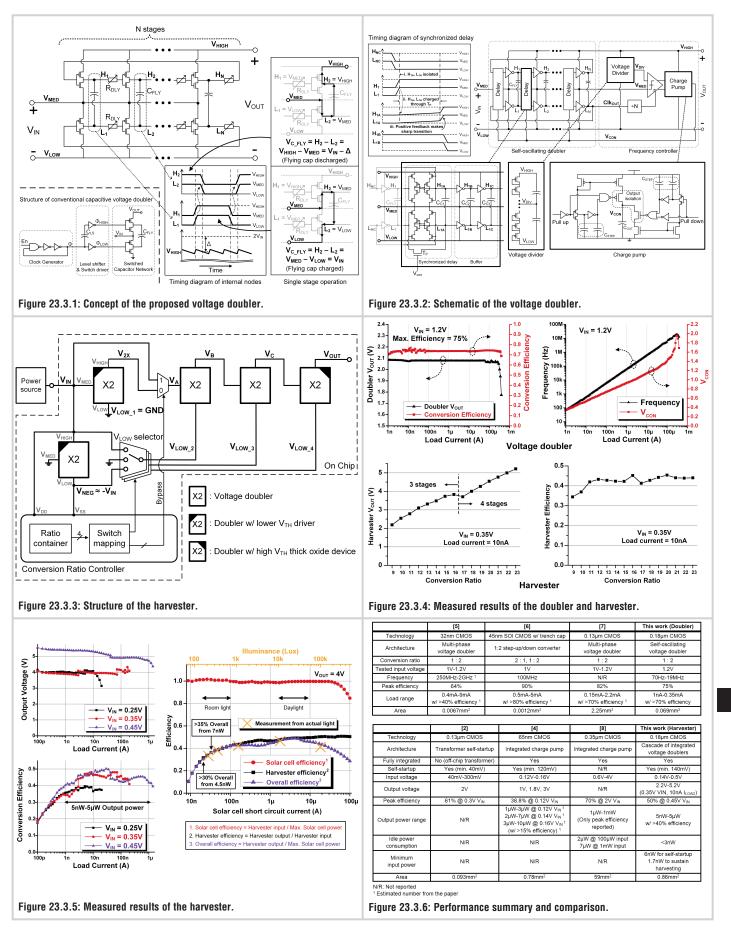

Figure 23.3.1 shows a conventional SC DC-DC voltage doubler that includes a clock generator, level shifter, and clock buffers. Each of these blocks introduces power overhead, reducing efficiency. The proposed doubler consists of two stacked ring oscillators with the output nodes of corresponding stages connected through flying caps ( $C_{\rm FLY}$ ). In each stage, inverters from the top and bottom ring either charge or discharge the flying cap thereby transferring power to the upper ring. Simultaneously, the inverters drive the next stage in their ring, creating a multi-phase DC-DC converter with overlapping charge/discharge phases and self-sustaining operation. Because the two oscillators are synchronized at every stage, phase mismatch is <0.01×FO4, reducing contention loss to <1% of switching loss (simulation) and avoiding the need for non-overlapping clocks.  $R_{\rm DLY}$  is a delay element that ensures matching of the flying cap charging/discharging time to the oscillation period. In the harvester, this delay is automatically tuned to balance switching and conduction losses and maintain optimum conversion efficiency across a range of load currents.

Figure 23.3.2 shows the detailed implementation of the voltage doubler. The delay element  $R_{\text{DLY}}$  consists of two coupled leakage-based delay elements [1] and a pass transistor  $T_{\text{P}}$ , followed by two buffers. When the inputs  $H_{\text{NC}}$  and  $L_{\text{NC}}$  of the stage switch from high to low, output nodes  $H_{1A}$  and  $L_{1A}$  (driven low) become isolated.  $T_{\text{P}}$  then provides a leakage path from  $L_{1}$  to  $L_{1A}$  that slowly raises  $L_{1A}$  and, through  $C_{\text{C1}}$ , also  $H_{1A}$ . Back-to-back inverters of the delay element provide positive feedback and amplify the transition once it reaches  $V_{\text{TH}}$ , creating a sharp edge. This transition is then buffered and passed to the next stage. The opposite transition functions similarly. Due to the output isolation the structure can produce very long, synchronized delay while the coupled positive feedback creates a sharp edge that limits short-circuit current and contention loss, enabling ultra-low power operation.

For each doubler, the delay tuning voltage  $V_{\text{CON}}$  is dynamically adjusted to balance conduction and switching losses by examining the ratio of output to input voltage ( $R_{\text{DIV}}$ ). A low  $R_{\text{DIV}}$  indicates a large voltage across the switches and dominant conduction loss. Conversely, high  $R_{\text{DIV}}$  indicates low conduction loss (zero as  $R_{\text{DIV}} \rightarrow 2$ ) and dominant switching losses. This property is used to modulate the oscillation frequency of the doubler and maintain optimum efficiency across load currents. A clocked comparator, operating at a fraction of

the internal oscillator frequency, takes in a divided form of the doubler output voltage ( $V_{\text{DIV}} = V_{\text{OUT}}/R_{\text{DIV\_DESIRED}}$ ) and the input voltage ( $V_{\text{MID}}$ ). The division ratio is configurable and is set to 1.73 in all measurements. A charge pump then takes in the corresponding pull-up/pull-down signals, and adjusts  $V_{\text{CON}}$  as needed to either speed or slow the oscillation. The voltage divider is implemented with a combination of a diode stack and capacitive divider to provide fast response and good low-frequency behavior.

Figure 23.3.3 shows the block diagram of the complete harvesting system, consisting of 4 stages of cascaded voltage doublers, a negative voltage generator, and circuits for conversion ratio control. A negative voltage is used to boost overall conversion ratio and to power control circuits, and is generated by connecting  $V_{\text{HIGH}}$  and  $V_{\text{MED}}$  of the doubler to  $V_{\text{IN}}$  and ground, respectively, resulting in  $V_{\text{NEG}}{\approx}{\sim}V_{\text{IN}}$  at the  $V_{\text{LOW}}$  port of the doubler. To facilitate energy harvesting from a low voltage source (e.g., photovoltaic cell under low light), the first stage and negative voltage generator use low  $V_{\text{TH}}$  (~300mV) devices for their flying cap drivers. Bootstrapping is also used with these low  $V_{\text{TH}}$  switches to improve  $I_{\text{OIV}}I_{\text{OFF}}$  at low input voltages. I/O devices are used in the final stage to protect the circuit from high voltages used to charge energy storage devices (e.g., batteries).

The conversion ratio is adjusted by changing the number of cascaded stages. In addition, we propose a new adjustment scheme where the  $V_{LOW}$  of a doubler is switched among  $V_{IN}$ , GND and  $V_{NEG}$ . If  $V_{LOW}$  is set to  $-V_{IN}$ , the voltage across the flying cap increases, resulting in  $V_{OUT}=(V_{MED}+V_{IN})\times 2-V_{IN}=2\times V_{MED}+V_{IN}$ . If  $V_{LOW}$  is set to GND for 4 cascaded stages, overall conversion ratio is 16×. However, if final stage  $V_{LOW}$  is set to  $V_{NEG}$ , overall conversion ratio increases by 1×, becoming 17×. Similarly, setting  $V_{LOW}$  to  $V_{IN}$  decreases conversion ratio. In a binary manner, the conversion ratio is controlled from 9× to 23×. Measured results in Fig. 23.3.4. demonstrate that a 0.35V input can be converted to a 2.2 to 5.2V voltage range with similar conversion efficiencies across settings.

To enable cold start of the complete system, the control logic operates between  $V_{\text{NEG}}$  and  $V_{\text{IN}}$  rails. Upon initial system startup,  $V_{\text{NEG}}$  and  $V_{\text{2X}}$  become available first and allow the control logic to turn on and configure the switches. As each stage is powered up, its internal frequency modulation is enabled and begins to control the frequency for optimum efficiency.

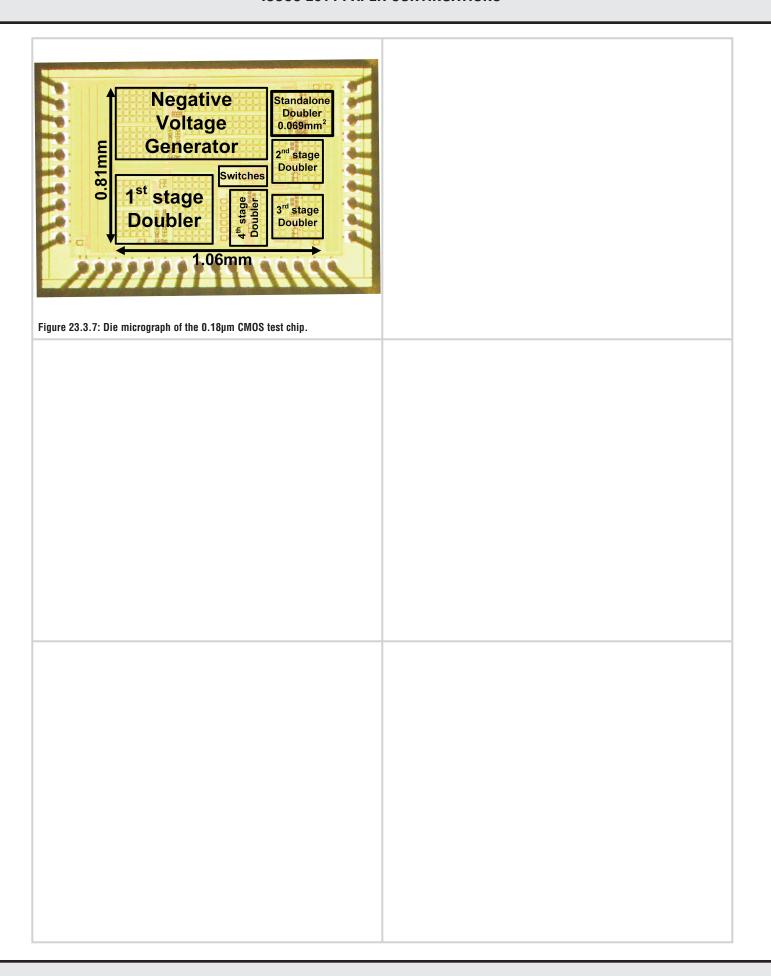

The voltage doubler and energy harvester are fabricated in 0.18µm CMOS (Fig. 23.3.7). Figure 23.3.4 shows a single doubler has >70% efficiency across 1nA to 0.35mA output current (>10⁵ range), with low idle power consumption of 170pW. Figure 23.3.5 shows measured results of the complete harvester. When  $V_{\text{IN}}$ =0.45V, the harvester delivers 5nW to 5µW output power with >40% efficiency, and has an idle power consumption <3nW. For  $V_{\text{IN}}$ =0.25V, corresponding to a solar cell under very low light, the harvester can take in between 10nW and 120nW to charge a ~4V battery voltage with >35% efficiency. Measured results with a small silicon solar cell (0.84mm²) show actual harvesting operation under dim light of <100lux. The harvester cold starts with <200lux of light and 6nW power source. Figure 23.3.6 summarizes the performance of the proposed design and compares it to prior work.

## References:

- [1] G. Chen, M. Fojtik, D. Kim, *et al.*, "Millimeter-Scale Nearly Perpetual Sensor System with Stacked Battery and Solar Cells," *ISSCC Dig. Tech. Papers*, pp. 288-289, Feb. 2010.

- [2] J.-P. Im, S.-W. Wang, K.-H. Lee, et al., "A 40mV Transformer-Reuse Self-Startup Boost Converter with MPPT Control for Thermoelectric Energy Harvesting," *ISSCC Dig. Tech. Papers*, pp. 104-105, Feb. 2012.

- [3] H. Shao, C.-Y. Tsui, and W.-H. Ki, "An Inductor-Less MPPT Design for Light Energy Harvesting Systems," *Proc. ASP-DAC*, pp. 101-102, Jan. 2009.

- [4] P.-H. Chen, K. Ishida, X. Zhang, *et al.*, "A 120-mV Input, Fully Integrated Dual-Mode Charge Pump in 65-nm CMOS for Thermoelectric Energy Harvester," *Proc. ASP-DAC*, pp. 469-470, Jan. 2012.

- [5] D. Somasekhar, B. Srinivasan, G. Pandya, *et al.*, "Multi-Phase 1 GHz Voltage Doubler Charge Pump in 32 nm Logic Process," *IEEE J. Solid-State Circuits*, vol. 45, no. 4, pp. 751-758, Apr. 2010.

- [6] L. Chang, R.K. Montoye, B.L. Ji, *et al.*, "A Fully-Integrated Switched-Capacitor 2:1 Voltage Converter with Regulation Capability and 90% Efficiency at 2.3A/mm²," *IEEE Symp. VLSI Circuits*, pp. 55-56, June 2010.

- [7] T.V. Breussegem and M. Steyaert, "A 82% Efficiency 0.5% Ripple 16-Phase Fully Integrated Capacitive Voltage Doubler," *IEEE Symp. VLSI Circuits*, pp. 198-199, June 2009.

- [8] I. Doms, P. Merken, R. Mertens, C. Van Hoof, "Integrated Capacitive Power-Management Circuit for Thermal Harvesters with Output Power 10 to 1000µW," *ISSCC Dig. Tech. Papers*, pp. 300-301, Feb. 2009.

## **ISSCC 2014 PAPER CONTINUATIONS**