# A Dual-Slope Capacitance-to-Digital Converter Integrated in an Implantable Pressure-Sensing System

Sechang Oh, Student Member, IEEE, Yoonmyung Lee, Member, IEEE, Jingcheng Wang, Student Member, IEEE, Zhiyoong Foo, Yejoong Kim, Member, IEEE, Wanyeong Jung, Student Member, IEEE, Ziyun Li, Student Member, IEEE, David Blaauw, Fellow, IEEE, and Dennis Sylvester, Fellow, IEEE

Abstract—A dual-slope capacitance-to-digital converter for pressure-sensing is presented and demonstrated in a complete microsystem. The design uses base capacitance subtraction with a configurable capacitor bank to narrow down input capacitance range and reduce conversion time. An energy-efficient iterative charge subtraction method is proposed, employing a current mirror that leverages the 3.6 V battery supply available in the system. We also propose dual-precision comparators to reduce comparator power while maintaining high accuracy during slope conversion, further improving energy efficiency. The converter occupies 0.105 mm<sup>2</sup> in 180 nm CMOS and achieves 44.2 dB SNR at 6.4 ms conversion time and 110 nW of power, corresponding to 5.3 pJ/conv-step FoM. The converter is integrated with a pressure transducer, battery, processor, power management unit, and radio to form a complete 1.4 mm $\times$  2.8 mm  $\times$  1.6 mm pressure sensor system aimed at implantable devices. The multi-layer system is implemented in 180 nm CMOS. The system was tested for resolution in a pressure chamber with an external 3.6 V supply and serial communication bus, and the measured resolution of 0.77 mmHg was recorded. We also demonstrated the wireless readout of the pressure data on the stack system operating completely wirelessly using an integrated battery.

Index Terms—Capacitance-to-digital converter, capacitive-sensor interface, integrating converter, pressure-sensing system, wireless sensor node.

## I. INTRODUCTION

MPLANTABLE systems are increasingly in demand for emerging biomedical applications, and yet they face stringent power budgets because battery capacity is limited due to their small volume [1], [2]. These systems collect and analyze sensor data, which is often measured in the form of capacitance. Capacitive sensor interfaces are widely used because of their inherent energy benefit; i.e., they do not draw static current, unlike resistive sensors. However, a capacitive-sensor interfacing circuit could dominate system power, and hence an energy-efficient capacitance-to-digital converter (CDC)

Manuscript received November 21, 2014; revised February 02, 2015, March 29, 2015, and May 15, 2015; accepted May 16, 2015. Date of publication June 11, 2015; date of current version June 23, 2015. This paper was approved by Guest Editor Marian Verhelst.

S. Oh, J. Wang, Z. Foo, Y. Kim, W. Jung, Z. Li, D. Blaauw, and D. Sylvester are with the University of Michigan, Ann Arbor, MI 48109 USA (e-mail: chaseoh@umich.edu).

Y. Lee is with Sungkyunkwan University, Suwon, Gyeonggi-do 440-746, South Korea.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2015.2435736

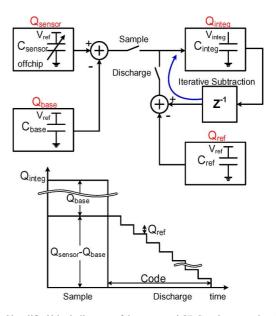

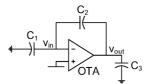

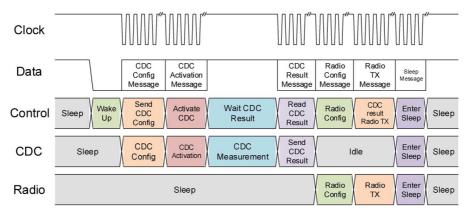

Fig. 1. Simplified block diagram of the proposed CDC and an associated waveform.

is required. Capacitive sensors, along with a corresponding CDC, are used in diverse applications such as pressure-sensing [3], humidity-sensing [4], proximity-sensing [5], and microphones [6].

Pressure-sensing is a key technique used in implantable devices with applicability to glaucoma treatment [2], [7], blood pressure monitoring [8], and tumor diagnosis, among others. These systems typically use a MEMS capacitive sensorand they require a moderate-resolution (9–10b), low-power CDC. Dual-slope converters are well known for their simplicity, accuracy, and low power consumption [9], [10]. However, their nominal base capacitance is often quite large compared to the capacitance changes due to pressure variations. The need to charge and discharge the large base capacitance in dual-slope CDCs (DS-CDC) makes it difficult to achieve sufficient resolution with high energy efficiency.

To address this challenge, we employ iterative charge subtraction/accumulation using a configurable capacitor bank to cancel base capacitance, and to zoom in and amplify the variable input region [4], [5]. This reduces the conversion time and energy for the DS-CDC (Fig. 1). The design also uses dual-precision comparators to achieve the high-resolution of a fine comparator with the low power consumption of a coarse comparator. It does this by enabling the fine comparator only in the final

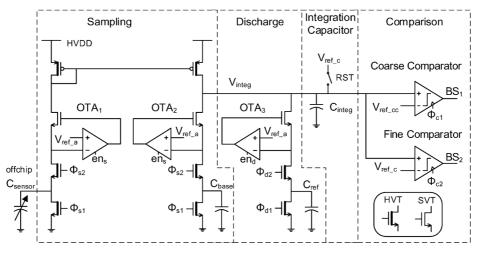

Fig. 2. Circuit diagram of the dual slope CDC

stages of conversion. The CDC has a low power consumption of 110 nW, which makes it compatible with ultra-small batteries that often suffer from low peak current capacity. We demonstrate CDC operation that is integrated with a complete pressure-sensing system using a MEMS pressure sensor, processor, memory, battery, and radio.

The remainder of the paper is structured as follows. Section II describes the proposed topology of the DS-CDC with a detailed description and analysis. Section III describes the implementation of the pressure-sensing system with the proposed CDC. Section IV presents CDC measurement results and demonstrates system operation, while Section V concludes the work.

# II. CAPACITANCE-TO-DIGITAL CONVERTER ANALYSIS AND IMPLEMENTATION

## A. Dual-Slope Operation

Fig. 1 shows a simplified block diagram of the proposed DS-CDC. The sampled charge difference between  $C_{

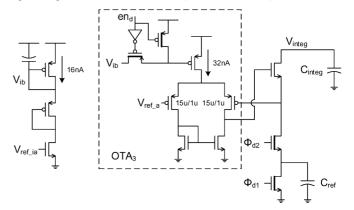

m sensor}$  and  $C_{\rm base}$  is transferred to  $C_{\rm integ}$ , and the transferred charge is removed by iterative subtraction using  $C_{\text{ref}}$ . The CDC circuit consists of a current mirror, charge subtraction/accumulation devices, and two comparators (shown in Fig. 2), followed by a ripple carry counter and digital control logic.

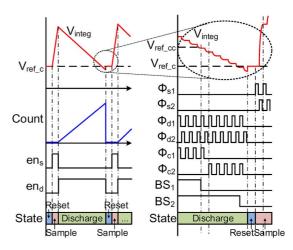

Fig. 3 shows the waveforms in the DS-CDC. During the reset state, all of the OTAs are disabled, and the RST switch is closed to set the voltage of  $C_{\rm integ}$  to  $V_{\rm ref\_c}$ . In the next sampling state, the  $OTA_1$  and  $OTA_2$  are enabled. While  $\Phi_{s1} = 1$ , the charge is removed from  $C_{\text{sensor}}$  and  $C_{\text{base}}$  by shorting both nodes of the capacitors to ground. With  $\Phi_{s2}=1$ , the top plate nodes of these capacitors are set to  $V_{\mathrm{ref\_a}}$  due to the feedback of the OTA and the device gated by  $\Phi_{s2}$ . Since  $\Phi_{s1}=0$  in this phase, all current conducted by the source followers is accumulated on  $C_{\text{sensor}}$  or  $C_{\rm base}$ . The OTAs drive the source followers to track  $V_{\rm ref\_a}$  with little error, and a current mirror above the source followers flips the direction of current from  $C_{\rm sensor}$ . As a result, the amount of transferred charge  $Q_{add}$  added to  $C_{integ}$  (4 pF) for each  $\Phi_s$ cycle is:

$$Q_{add} = (C_{\text{sensor}} - C_{\text{base}}) \times V_{\text{ref a}} \tag{1}$$

Fig. 3. CDC waveforms.

The full sampling operation consists of  $4\Phi_s$  cycles, during which  $4Q_{add}$  is transferred, thus providing  $4\times$  charge amplification.

In the following discharge state, OTA<sub>3</sub> and one of the two comparators is turned ON. Similarly, the amount of charge that is subtracted from  $C_{\text{integ}}$  for each  $\Phi_c$  cycle (denoted  $Q_{sub}$ ), and the value of  $V_{integ}$  at the end of nth cycle of the discharge stage are given by:

$$Q_{sub} = C_{ref} \times V_{ref\_a} \tag{2}$$

$$Q_{sub} = C_{ref} \times V_{ref\_a}$$

$$V_{integ}(n) = V_{ref\_c} + \frac{4Q_{add} - n \cdot Q_{sub}}{C_{integ}}$$

(2)

$C_{\rm ref}$  (18 fF) is composed of two MIM capacitors in series. The discharge state ends when  $V_{integ}$  becomes smaller than  $V_{ref\_c}$ ; the total number of required cycles is recorded by a ripple carry counter as the digital code.

$$Code = 4Q_{add}/Q_{sub} = 4(C_{sensor} - C_{base})/C_{ref}$$

(4)

In the proposed CDC,  $C_{\rm sensor}$  is an off-chip sensor capacitor, and  $C_{\mathrm{base}}$  is a programmable on-chip MIM capacitor bank composed of capacitors and NMOS switches, allowing for adjustment of the capacitance measurement range. V<sub>ref\_a</sub> is 300 mV

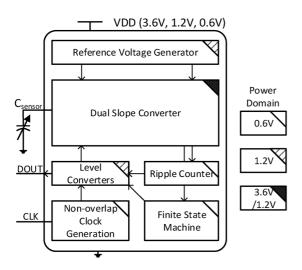

Fig. 4. Block diagram of the CDC with power domain.

and each  $C_{\rm base}$  has a 4 pF linear range, and thus the maximum  $4Q_{add}$  difference is 4.8 pC between the smallest and largest inputs from (1).  $\Delta V_{\rm integ}$  and  $\Delta C_{\rm ode}$  are 1.2 V and 890 from (3) and (4), respectively, and the LSB voltage is 1.35 mV. Although  $C_{sense}$  and  $C_{\rm base}$  can be larger than  $C_{\rm integ}$  since both  $C_{sense}$  and  $C_{\rm base}$  are simultaneously clocked,  $V_{\rm integ}$  is not saturated as long as  $4 \cdot (C_{sense} - C_{\rm base}) < C_{\rm integ}$ . The sensor capacitance changes due to an environment signal such as pressure. Because environmental signals change fairly slowly, a slow speed is typically acceptable for CDCs. Clocks  $\Phi_{\rm s1}/\Phi_{\rm s2}$  and  $\Phi_{\rm d1}/\Phi_{\rm d2}$  are non-overlapping 125 kHz clock pairs. To save power, 0.6 V is used for non-overlapping clock generation and digital control logic. When the 0.6 V signals pass on to the 1.2 V domain, level converters are used to shift up the voltage domain (Fig. 4).

# B. Energy-Efficient Charge Subtraction

The OTAs are responsible for a significant portion of the CDC's total energy consumption, and so its bandwidth should be appropriately chosen to optimize energy. Unity gain bandwidth  $(\omega_u)$  of an OTA is generally  $g_{m,OTA}/C_L$  for a single-stage design where  $g_{m,OTA}$  is the transconductance of the OTA input transistor pair and  $C_L$  is the OTA output load capacitance. The unity gain bandwidth is unchanged even when the OTA forms a negative feedback loop  $(\omega_{u,cl}=\omega_u)$ . Its transfer function is  $A_{0,cl}/(1+s/\omega_{p,cl})$  [11], where  $A_{0,cl}$  and  $\omega_{p,cl}$  are the DC gain and the dominant pole of the loop, respectively. Assuming the DC OTA gain is much larger than the inverse of the feedback factor  $(A_0\gg 1/\beta)$ ,  $A_{0,cl}$  and  $\omega_{p,cl}$  are approximated as  $1/\beta$  and  $\beta g_{m,OTA}/C_L$ . The settling time constant of the first order system is the inverse of  $\omega_{p,cl}$ :

$$\tau = \frac{C_L}{\beta g_{m,OTA}} \tag{5}$$

When the feedback is capacitive, as shown in Fig. 5,  $C_L$  becomes equal to  $C_3+C_1C_2/(C_1+C_2)$  and  $1/\beta$  is  $(C_1+C_2)/C_2$ . Assuming  $C_3\ll C_1,C_2$ , the settling time constant becomes:

$$\tau \cong \frac{C_1}{g_{m,OTA}} \tag{6}$$

Fig. 5. Capacitive feedback of an OTA (switches not shown).

Fig. 6. Discharge circuit schematic.

From this we see that  $\tau$  is not related to the feedback capacitor  $(C_2)$ , and only depends on the input capacitor  $(C_1)$ .

The proposed DS-CDC opens the sensor capacitor path while only connecting the  $C_{\text{ref}}$  path during the discharge state as shown in Fig. 2 and Fig. 6. The corresponding  $\tau$  is  $C_{\text{ref}}/g_{m,OTA}$ .  $C_{\text{ref}}$  is equivalent to the LSB of the DS-CDC. Hence  $C_{\text{ref}}$  is much smaller than  $C_{\text{sensor}}$ , allowing for significantly lower OTA tail current for a fixed sampling rate. In the proposed method, the OTA's feedback loop is modified to include a source follower, which isolates the discharge path from  $C_{

m integ}$  as well as  $C_{

m sensor}$ . The OTAs in the proposed design use a single-stage design. The OTA bias current (Fig. 6 left) is generated by a voltage reference described later. Although the OTAs use a 1.2 V supply, the current mirror uses 3.6 V, which is available in the complete microsystem described later (battery voltage); this increases  $V_{\rm integ}$  range while keeping power low. Although the proposed CDC has an energy benefit, mismatch in the current mirror and injection at the switches can result in offsets and gain errors. These need to be calibrated for each  $C_{\rm base}$  to obtain a complete, calibrated code over the entire range of the CDC. The power supply rejection is also limited in the proposed design and the CDC may require a supply regulator.

## C. Noise Analysis and Dual Comparators

The CDC resolution is determined by the circuit noise, which is composed of sampling state noise and discharge state noise.

The sampling noise comes from the switched-capacitor integrators. In a typical implementation, as shown in Fig. 5, the input-referred noise is represented by  $\overline{v_{n,c1}^2} = 7kT/3C_1$  and the output noise is described as  $\overline{v_{n,o}^2} = 7kT/3C_1 \cdot C_1^2/C_2^2$ . Here the OTA transconductance is assumed to be much lower than the switch transconductance [11]. Although the OTA output noise power spectrum density is proportional to  $1/g_{m,OTA}$ , the OTA bandwidth is proportional to  $g_{m,OTA}$ , and hence the

Fig. 7. Clocked comparator schematic.

sampled noise of the switched capacitor integrator is independent of  $g_{m,OTA}$ . This equation also applies for the proposed CDC. The noise from the sensor capacitor on the integration capacitor using the proposed OTA feedback is represented by:

$$\overline{v_{n,\text{OTA,sensor}}^2} = \frac{7kTC_{\text{sensor}}}{3C_{\text{integ}}^2} \tag{7}$$

In the worst-case condition where the largest  $C_{\mathrm{sensor}}$  is used (30.7 pF), the noise is 136  $\mu$ Vrms. The current mirror noise can be suppressed by proper transistor sizing (large length). Similarly, the noise from  $C_{\mathrm{base}}$  on  $C_{\mathrm{integ}}$  ( $v_{n,\mathrm{OTA,base}}$ ) is 115  $\mu$ Vrms (with 22 pF  $C_{\mathrm{base}}$ ). The noise from  $C_{\mathrm{ref}}$  on  $C_{\mathrm{integ}}$  ( $v_{n,\mathrm{OTA,ref}}$ ) is 3.2  $\mu$ Vrms; this is negligible and hardly affects the discharge noise.

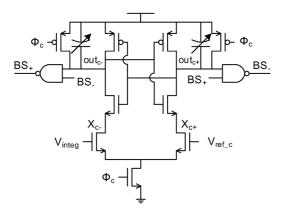

The CDC uses clocked comparators (Fig. 7). The comparator precharges both  $out_c$  nodes and  $X_c$  nodes to 1 with  $\Phi_c=0$ . When  $\Phi_c=1$ , the comparator discharges those nodes with input dependent speeds and makes a comparison decision using regenerative feedback. The main noise source of the clocked comparator is thermal noise in our simulation; this causes a random decision error and the error probability follows Gaussian statistics [12].

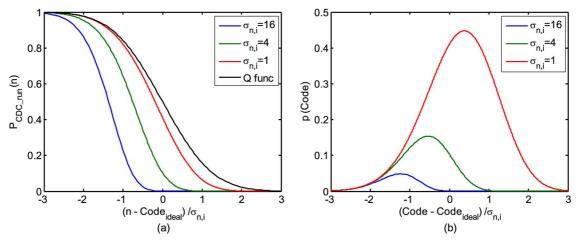

In the proposed DS-CDC, the probability of obtaining a 1 as a function of the comparator input x can be written in the form of the Q function [13]:

$$P_1(x) = \int_{-\pi}^{\infty} \frac{1}{\sqrt{2\pi} \cdot \sigma_{n,i}} e^{-\frac{x^2}{2\sigma_{n,i}^2}} dx = Q\left(\frac{x}{\sigma_{n,i}}\right)$$

(8)

where x is the comparator input normalized to LSB, and  $\sigma_{n,i}$  is the input-referred comparator noise normalized to LSB. The discharge process of the CDC involves discrete and sequential events. Initially, the counter value is 0, and it counts every comparison until the comparator flips. The first flip of the comparator directly indicates the end of the conversion, while continuing iterations of the CDC imply the comparator has not yet flipped, and all previous results were 1's. The probability that the CDC is still performing a conversion at the nth cycle  $(P_{CDCrun})$  is the cumulative product of  $P_1(x)$ :

$$P_{CDCrun}(n) = \prod_{i=0}^{n} P_1(i - Code_{ideal}) = \prod_{i=0}^{n} Q\left(\frac{i - Code_{ideal}}{\sigma_{n,i}}\right)$$

(9)

where  $Code_{ideal} = 4(C_{sensor} - C_{base})/C_{ref}$ . From (9), the probability density function of the code (final iteration cycle of the CDC conversion) is:

$$p(Code) = P_{\text{CDCrun}}(Code - 1) - P_{\text{CDCrun}}(Code)$$

$$= \left(1 - Q\left(\frac{Code - Code_{\text{ideal}}}{\sigma_{n,i}}\right)\right) \cdot \prod_{i=0}^{n-1} Q\left(\frac{i - Code_{\text{ideal}}}{\sigma_{n,i}}\right).$$

(10)

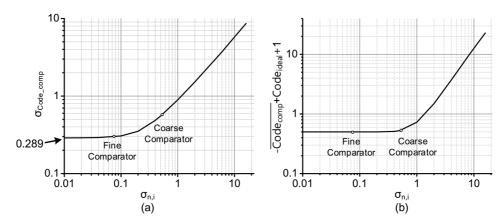

Equations (9) and (10) can be numerically solved, and they are shown with example values in Fig. 8. From (10), the expectation value and variation of Code are calculated as:

$$\overline{Code_{\text{comp}}} = E[Code] = \sum Code \cdot p(Code) \tag{11}$$

$$\sigma_{Code_{\text{comp}}}^2 = Var[Code] = \sum Code^2 \cdot p(code) - \overline{Code_{\text{comp}}^2} \tag{12}$$

Fig. 9 shows calculated  $\overline{Code_{\mathrm{comp}}}$  and  $\sigma_{Code_{\mathrm{comp}}}$  with respect to  $\sigma_{n,i}$ . When  $\sigma_{n,i} \ll 1$  (ideal comparator),  $\sigma_{Code_{\mathrm{comp}}}$  converges to  $0.289 \, (\cong 1\sqrt{12})$  representing quantization noise, and  $\overline{Code_{\mathrm{comp}}}$  converges to  $Code_{\mathrm{ideal}} + 0.5$  as expected since comparator flip probability is 0.5 at  $Code = Code_{\mathrm{ideal}}$ . When  $\sigma_{n,i} \gg 1$ ,  $\overline{Code_{\mathrm{comp}}}$  and  $\sigma_{Code_{\mathrm{comp}}}$  converge to linear expressions.

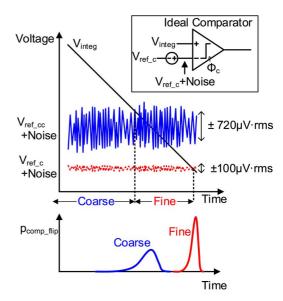

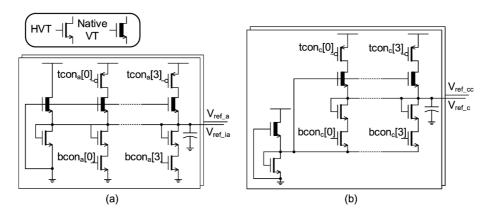

Comparator energy consumption is reduced by adopting a dual comparator scheme, composed of a coarse comparator and a fine comparator, without impacting the CDC accuracy (Fig. 2 and Fig. 10). For the energy reduction, the lower power coarse comparator is used for the most discharge cycles. After the flip of the coarse comparator, the fine comparator makes the final decision that  $V_{\rm integ} < V_{\rm ref\_c}$  and determines overall accuracy. To accomplish this, the coarse comparator requires a higher reference voltage (V<sub>ref\_cc</sub>) than the fine comparator  $(V_{ref_c})$  as shown in Fig. 10. The difference can be generated by two different voltage references. The coarse comparator design  $(720 \,\mu\text{V} \text{ rms input-referred noise}, 7.4 \,\text{fJ/comparison}, \text{simulated})$ is constrained by minimum size transistors. The fine comparator (100  $\mu$ Vrms noise, 450 fJ/comparison, simulated) is designed for  $\sigma_{n,i} = 0.1$  with  $10 \times$  larger transistors and output capacitors to balance energy and noise. The converted comparison-output noises  $(V_{\rm LSB} \cdot \sigma_{Code_{\rm comp}}, V_{\rm LSB} = C_{\rm ref}/C_{\rm integ}.V_{\rm ref\_a})$  are 780  $\mu$ Vrms (coarse comparator) and 402  $\mu$ Vrms (fine comparator, dominated by quantization noise). The reference voltages  $V_{ref\_a}$  and  $V_{ref\_ia}$  (300 mV for OTAs) as well as  $V_{\rm ref\_c}$  and  $V_{\rm ref\_cc}$  (600 mV for comparators) are generated using ultra-low power (60 pW) voltage references. V<sub>ref\_a</sub>  $(V_{\mathrm{ref}\_ia})$  is approximately equal to the threshold voltage difference of two different-type transistors (Fig. 11(a)), and the higher reference voltages (V<sub>ref\_c</sub> and V<sub>ref\_c</sub>) are generated by stacking the two references (Fig. 11(b)) [14]. The references have <2 mV resolution programmability by trimming tconand bcon. Each reference voltage is connected to a decoupling capacitor (4 pF). The trimming methodology consists of two steps: We initially use a large voltage difference between the two references and measure the resolution, which is determined by the fine comparator. Then, we incrementally lower the threshold voltage difference until resolution starts to degrade and select the last voltage difference where resolution was

Fig. 8. (a) Probability that the CDC is still performing a conversion at the nth cycle. (b) Probability density function of the code.

Fig. 9. (a) Comparison output noise. (b) Comparison output offset calculated from the comparator flip probability.

still maintained. This methodology ensures fine-comparator resolution with minimum power consumption. In simulation, a 2–4 mV comparator offset difference is sufficient to achieve the resolution of the fine comparator and results in an average usage of the fine comparator of three cycles per conversion. In the test-chip implementation it was not possible to measure the minimum necessary comparator offset difference due to a step size limitation in the testing harness.

The total noise power is calculated by adding the OTA noises and the comparator noise:

$$\overline{v_n^2} = 4\overline{v_{n,\text{OTA,sensor}}^2} + 4\overline{v_{n,\text{OTA,base}}^2} + \overline{v_{n,\text{comp}}^2}$$

(13)

where  $\overline{v_{n,\mathrm{comp}}^2} = V_{\mathrm{LSB}}^2 \cdot \sigma_{Code_{\mathrm{comp}}}^2$ . Based on the design values,  $v_{n,rms}$  is calculated to 537  $\mu\mathrm{Vrms}$ ; this corresponds to 7.2 fF resolution. Quadruple sampling was chosen to balance the sampling noise and the discharge noise.

# III. SYSTEM INTEGRATION

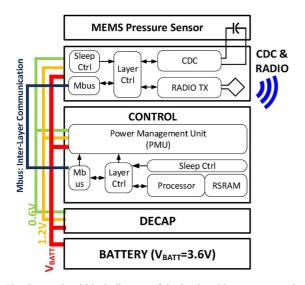

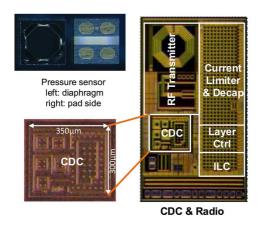

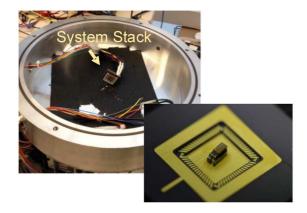

The proposed CDC was integrated in a complete pressure sensing system constructed from stacked IC layers to demonstrate CDC operation in an ultra-low power sensor platform [1]. Fig. 12 shows a system-level block diagram.

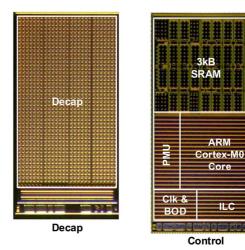

The system is powered by a custom 2  $\mu$ Ah thin-film battery with 3.6 V output, which is down-converted to 1.2 V and 0.6 V by a switched-capacitor-based power management unit (PMU)

Fig. 10. Dual comparators operating concept.

in the control layer. The DS-CDC uses all three power domains: 0.6 V for digital control logic and non-overlapping clock generator, 1.2 V for most analog blocks, and 3.6 V for the current mirror. The system also includes an ARM Cortex-M0 processor and 3 kB low-power retentive (always powered on) memory

Fig. 11. 60 pW reference voltage generator for (a) the OTAs and (b) the comparators.

Fig. 12. System-level block diagram of the implantable pressure monitoring sensor with the proposed CDC.

in the control layer, which controls overall system operation. An on-off keying (OOK) near-field radio [2] with an on-chip coil is located on the top IC layer to enable users to collect the measured pressure data. The proposed CDC is also located on the top IC layer. The processor on the control layer communicates with the radio and CDC via an inter-layer communication (ILC) bus. A layer dedicated to providing decoupling capacitance (decap layer) is also included to ensure the supply voltages remain stable.

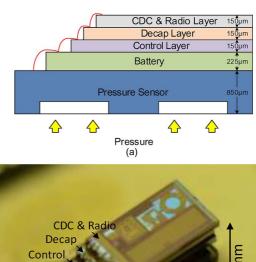

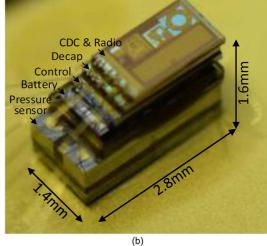

The entire electronics stack is placed on a MEMS pressure sensor whose two top electrodes are connected to the CDC with bondwires, as shown in Fig. 13. The sensing diaphragm of the MEMS pressure sensor faces the bottom of the stack so that it can be exposed to the ambient pressure when the upper part of the sensing system is sealed. The entire stack measures  $1.4 \text{ mm} \times 2.8 \text{ mm} \times 1.6 \text{ mm}$ , allowing minimally invasive implantation, potentially with a syringe. Fig. 14 shows die micrographs for each of the implemented IC layers.

## IV. MEASUREMENT RESULTS

The CDC is implemented in 180 nm CMOS, and has an active area of 0.105 mm<sup>2</sup>. To test CDC linearity, the bottom voltage

Fig. 13. (a) Physical structure diagram and (b) picture without encapsulation of the proposed implantable sensing system.

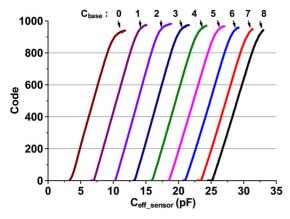

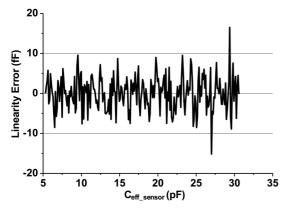

of  $C_{\rm sensor}$  is swept and  $C_{\rm sensor} \cdot (V_{\rm ref\_a} - V_{\rm sens\_bot})/V_{\rm ref\_a}$  is regarded as effective capacitance  $(C_{\rm eff\_sensor})$ . While this test does not include the effect of the OTA loading changes, it is capable of verifying the whole range continuously. Fig. 15 shows the measurement result. By changing the  $C_{\rm base}$  configuration from 0 to 8, which corresponds to 0 pF to 22 pF, the CDC covers  $C_{\rm eff\_sensor}$  ranging from 5 pF to 31 pF. A linearity error plot shown in Fig. 16 combines results from 9 different ranges calibrated by 2 points in each range. Maximum error is found to be 16.5 fF. The ranges are configured to overlap with an adjacent  $C_{\rm base}$  value to avoid missing codes. For a given  $C_{\rm base}$ ,

Fig. 14. Implemented IC layers and MEMS pressure sensor.

Fig. 15. Code versus effective sensor capacitor  $(C_{

m eff\_sensor})$  using voltage sweep with various  $C_{\text{base}}$  values.

Fig. 16. Linearity error of the proposed DS-CDC with 9 different  $C_{\rm base}$ .

a 4 pF range is measured with a linearity that is less than the maximum error.

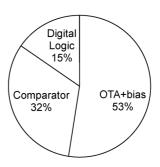

Power and resolution are measured at the worst-case maximum input capacitance condition. Total CDC power is 112 nW, consuming 95 nW from 1.2 V, 17 nW from 0.6 V, and 0 nW from 3.6 V, and the power breakdown is shown in Fig. 17. This makes it suitable for miniature sensor node systems that often have batteries with low peak current capabilities [15]. Power from the 1.2 V supply is reduced by

Core

Fig. 17. Power breakdown of the CDC.

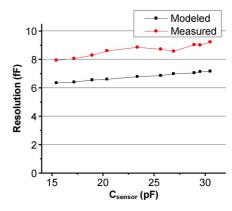

Fig. 18. Modeled and measured capacitance resolution.

13% when using the proposed dual-comparator method rather than using the fine comparator only. Power savings are limited by the parasitic capacitance on the clock network. The CDC  $^{'}Capacitance\,Subrange/2\sqrt{2}$ SNR is defined as  $20\log$  (  $Capacitance\ Resolution$ the figure of merit (FoM) is  $\frac{(Power \times Meas.Time)}{2^{(SNR-1.76)/6.02}}$ . Here,  $2\sqrt{2}$ is the crest-factor [16] for DC-input CDC to compare with sinusoidal-input ADCs. This SNR definition imagines that a sinusoidal continuous capacitance is given as an input with an amplitude of Capacitance Subrange/2, and the signal rms is regarded as Capacitance Subrange/ $2\sqrt{2}$ . The measured capacitance resolution is 8.7 fF, resulting in 5.3 pJ/conv-step FoM. Fig. 18 shows the measured resolution and the modeled resolution with different  $C_{\rm sensor}$ . The measured capacitance

|                       | This              |           |          |             |         |         |          |                   |         |                      |

|-----------------------|-------------------|-----------|----------|-------------|---------|---------|----------|-------------------|---------|----------------------|

|                       | Work              | [4]       | [5]      | [9]         | [10]    | [19]    | [20]     | [21]              | [22]    | [23]                 |

| Technology(μm)        | 0.18              | 0.16      | 0.35     | 0.35        | 0.35    | 0.13    | 0.32     | 0.18              | 0.18    | 0.04                 |

|                       | Dual              |           |          |             |         |         |          |                   |         |                      |

| Method                | Slope             | ΣΔ        | ΣΔ       | PWM         | PWM     | Freq    | PWM      | SAR               | ΣΔ      | IDCD <sup>4</sup>    |

| Input Range(pF)       | 5.3-30.7          | 0.54-1.06 | 8.4-11.6 | 1-6.8       | 0.8-1.2 | 6.0-6.3 | 0.5-0.76 | 2.5-75.3          | 0-24    | 0.7-10000            |

| Meas. Time(ms)        | 6.4               | 0.8       | 0.02     | 7.6         | 0.05    | 1       | 0.033    | 4                 | 0.23    | 0.0195               |

| Power                 | 110 nW            | 10.3 μW   | 14.9 mW  | $210~\mu W$ | 15.8 mW | 270 nW  | 84 μW    | 160 nW            | 33.7 μW | 1.84 μW <sup>5</sup> |

| SNR <sup>1</sup> (dB) | 44.2 <sup>3</sup> | 68.4      | 84.8     | 83          | 45.7    | 29.4    | 40.9     | 55.4 <sup>3</sup> | 94.7    | 49.75                |

| FoM²(pJ/c·s)          | 5.3 <sup>3</sup>  | 3.8       | 21       | 140         | 5000    | 11      | 98       | $1.3^{3}$         | 0.18    | 0.145                |

TABLE I PERFORMANCE SUMMARY AND COMPARISON WITH RECENTLY PUBLISHED CDCs

- $\begin{array}{|c|c|c|c|c|}\hline 1 & SNR = 20 \log \left(\frac{Capacitance\ Range/2\sqrt{2}}{Capacitance\ Resolution}\right) \\ 2 & FoM = \frac{PowerXMeas.Time}{2(SNR-1.76)/6.02}. \end{array}$

- <sup>3</sup> Calculated with one subrange.

- <sup>4</sup> Iterative delay-chain discharge.

- <sup>5</sup> Measured with 11.3 pF.

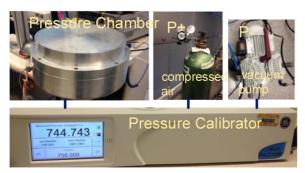

Fig. 19. Pressure measurement set-up for the CDC integrated in an implantable pressure sensing system.

resolution is within 20% of the estimated resolution from (13), providing reasonable matching between theory and experiment. Table I summarizes CDC performance and compares with the previously reported CDCs.

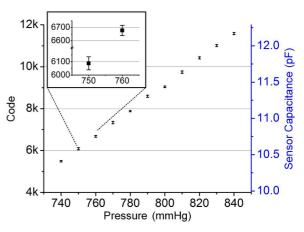

The proposed CDC is integrated in a pressure-sensing system as described in Section III and tested as a pressure sensor. Fig. 19 shows the test set-up for pressure measurement. The sensing system is wirebonded to a PGA socket and it was placed in an aluminum pressure chamber. The pressure inside the chamber was controlled by a pressure calibrator where compressed air and vacuum are supplied externally. Using the bonded wires, an external 3.6 V supply overrode the battery, and the ILC bus read the CDC data. Fig. 20 shows the pressure

Fig. 20. Pressure measurement result with  $C_{\rm base} = 4$  and 32 OSR, taken using the complete pressure-sensing system in a pressure chamber.

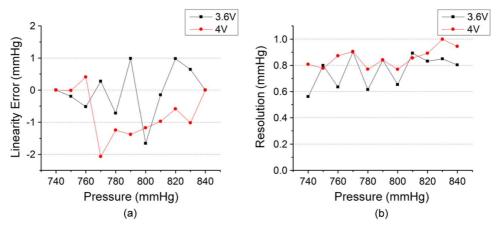

measurement results achieving a linear output response with  $R^2 = 0.9995$ . The chamber pressure was swept from 740 to 840 mmHg, which is a sufficient range for various body pressure diagnoses, including intra-ocular, intra-cranial, and intra-abdominal pressures [17]. The MEMS pressure sensor used in this experiment has high linearity in this region [18], and the corresponding capacitance range is overlaid in Fig. 20. During this test,  $C_{\text{base}}$  was set to 4, and Code is the total count. The measured power sensitivity of the system was 0.4 mmHg/mV for 3.6 V and 4.0 V supplies without calibration. During the system measurement, the PMU generated relatively large fluctuations on the power supply nodes and the processor was also running introducing possible additional noise. Given the sensitivity of the CDC to supply variation, the CDC was operated with an over-sampling rate (OSR) of 32 and achieved a resolution of 0.77 mmHg with 200 ms conversion time. The long-term CDC supply sensitivity can bead dressed with two-pressure-point calibration as its linearity is preserved across voltage. Since a pressure sweep during calibration represents the most time-consuming and expensive process, multiple readings can be taken at different supply voltages for each pressure and then stored in a look-up table. In operation, a low sample rate ADC would read the supply voltage to index

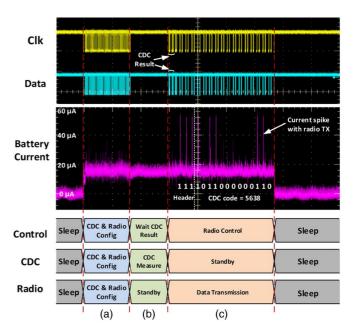

Fig. 21. Pressure sensing system measurement. (a) Linearity error with two-pressure-point correction. (b) RMS resolution for 3.6 V and 4.0 V operation.

Fig. 22. Operation sequence of the implantable pressure-sensing system.

into the look-up-table. Using this manner of two-pressure-point correction, the linearity error and resolution become less than 2 mmHg and 1 mmHg, respectively, for 3.6 V and 4.0 V supply across 740 to 840 mmHg as shown in Fig. 21 with fairly small added testing time and cost beyond a single-Vdd dual-pressure calibration. However, since a low sampling rate ADC was not available in our system at the time of testing, the system level performance and power overhead of this supply voltage calibration was not quantified.

Fig. 22 shows an example operation scenario of the sensing system. The sensor system typically spends most of its time in a low-power sleep mode (<8 nW) to save power. Then it periodically wakes up and enters active mode ( $\sim 50 \ \mu W$ ) for measurement operation. As the system wakes up, it first initializes the CDC and then initiates pressure measurement. Upon completion, the digital pressure value is stored to memory and can be accessed for later radio transmission. In this example, the data is immediately transmitted through the radio after each pressure measurement. The system then returns to sleep mode. Each pressure measurement cycle consumes 6.5  $\mu$ J, and so the 2  $\mu$ Ah battery corresponds to 17.7 days of operation capacity (assuming the pressure is recorded every 10 minutes). Fig. 23 shows measured waveforms of the ILC wires and battery current. The ILC activity indicates the processor in the control layer is interacting with the CDC and the radio on the top IC layer. As the system wakes from the low power sleep

Fig. 23. Measured waveforms for the sensing system operation.

mode, the current consumption jumps to  $\sim 20~\mu A$ . The ILC activity in part (a) indicates that the CDC is configured, and pressure measurement is activated. During the CDC activation

in part (b), no ILC activity is required until the result is sent back to the memory in the early part of (c). In the remainder of part (c), the processor controls the radio to send out pulses; whenever the radio transmits a pulse, a battery current spike can be clearly observed. After the radio transmission, the current consumption drops to <8 nA as the system enters sleep mode to save power.

#### V. CONCLUSIONS

This paper proposed an energy-efficient DS-CDC suitable for implantable pressure sensing systems. Pressure sensors often have large base capacitance, while their variation is small. The CDC removes this base capacitance using a configurable capacitor bank that zooms in on the capacitance variation and reduces conversion time and energy. The CDC uses three different supply voltages (0.6, 1.2, 3.6 V) that are available in the system to optimize energy. By isolating the reference capacitance from the relatively large neighboring sensor capacitor, the OTA bias current can be reduced to 32 nA. Dual-precision comparators are used in conjunction to achieve the high resolution of the fine comparator and low energy of the coarse comparator. The proposed CDC achieves 8.7 fF resolution, 5.3 pJ/conv-step FoM, which is in reasonable agreement with the theoretical noise analysis for the circuit. In addition, we demonstrated a complete  $1.4~\text{mm} \times 2.8~\text{mm} \times 1.6~\text{mm}$  pressure sensor system with a MEMS pressure sensor, processor, memory, PMU, battery, ILC, and radio. This system was tested in a pressure chamber with an external 3.6 V supply and OSR of 32 and achieved 0.77 mmHg resolution with good linearity ( $R^2 = 0.9995$ ).

## ACKNOWLEDGMENT

The authors acknowledge Advotech Co. Inc. for stack assembly, and the Cymbet Co. and Murata Electronics Oy for battery and pressure sensor manufacturing, respectively.

### REFERENCES

- [1] Y. Lee *et al.*, "A modular 1 mm<sup>3</sup> die-stacked sensing platform with low power I<sup>2</sup>C inter-die communication and multi-modal energy harvesting," *IEEE J. Solid-State Circuits*, vol. 48, no. 1, pp. 229–243, Jan. 2013.

- [2] H. Ghaed et al., "Circuits for a cubic-millimeter energy-autonomous wireless intraocular pressure monitor," *IEEE Trans. Circuits Syst. I*, vol. 60, no. 12, pp. 3152–3162, Dec. 2013.

- [3] S. Oh et al., "Dual-slope capacitance to digital converter integrated in an implantable pressure sensing system," in Proc. Eur. Solid-State Circuits Conf. (ESSCIRC), 2014, pp. 295–298.

- [4] Z. Tan, R. Daamen, A. Humbert, Y. Ponomarev, Y. Chae, and M. Pertijs, "A 1.2-V 8.3-nJ CMOS humidity sensor for RFID applications," IEEE J. Solid-State Circuits, vol. 48, no. 10, pp. 2469–2477, Oct. 2013.

- [5] S. Xia, K. Makinwa, and S. Nihtianov, "A capacitance-to-digital converter for displacement sensing with 17b resolution and 20 µs conversion time," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, 2012, pp. 198–200.

- [6] S. Jawed, D. Cattin, M. Gottardi, N. Massari, A. Baschirotto, and A. Simoni, "A 828 μW 1.8 V 80 dB dynamic-range readout interface for a MEMS capacitive microphone," in *Proc. Eur. Solid-State Circuits Conf. (ESSCIRC)*, 2008, pp. 442–445.

- [7] E. Chow, S. Chakraborty, W. Chappell, and P. Irazoquil, "Mixed-signal integrated circuits for self-contained sub-cubic millimeter biomedical implants," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, 2010, pp. 236–237.

- [8] P. Cong, N. Chaimanonart, W. Ko, and D. Young, "A wireless and batteryless 10-bit implantable blood pressure sensing microsystem with adaptive RF powering for real-time laboratory mice monitoring," *IEEE J. Solid-State Circuits*, vol. 44, no. 12, pp. 3631–3644, Dec. 2009.

- [9] Z. Tan, S. Shalmany, G. Meijer, and M. Pertijs, "An energy-efficient 15-bit capacitive-sensor interface based on period modulation," *IEEE J. Solid-State Circuits*, vol. 47, no. 7, pp. 1703–1711, Jul. 2012.

- [10] P. Bruschi, N. Nizza, and M. Piotto, "A current-mode, dual slope, integrated capacitance-to-pulse duration converter," *IEEE J. Solid-State Circuits*, vol. 42, no. 9, pp. 1884–1891, Sep. 2007.

- [11] R. Schreier, J. Silva, J. Steensgaard, and G. Temes, "Design-oriented estimation of thermal noise in switched-capacitor circuits," *IEEE Trans. Circuits Syst. I*, vol. 52, no. 11, pp. 2358–2368, Nov. 2005.

- [12] J. Kim, B. Leibowitz, J. Ren, and C. Madden, "Simulation and analysis of random decision errors in clocked comparators," *IEEE Trans. Circuits Syst. I*, vol. 56, no. 8, pp. 1844–1857, Aug. 2009.

- [13] M. Pelgrom, Analog-to-Digital Conversion. New York, NY, USA: Springer-Verlag, 2013.

- [14] M. Seok, G. Kim, D. Blaauw, and D. Sylvester, "A portable 2-transistor picowatt temperature-compensated voltage reference operating at 0.5 V," *IEEE J. Solid-State Circuits*, vol. 47, no. 10, pp. 2534–2545, Oct. 2012

- [15] Cymbet Corp. [Online]. Available: http://www.cymbet.com

- [16] Y. Chae, K. Souri, and K. Makinwa, "A 6.3 μW 20 bit incremental zoom-ADC with 6 ppm INL and 1 μV offset," *IEEE J. Solid-State Circuits*, vol. 48, no. 12, pp. 3019–3027, Dec. 2013.

- [17] L. Yu, B. Kim, and E. Meng, "Chronically implanted pressure sensors: Challenges and state of the field," *Sensors*, vol. 14, no. 11, pp. 20620–20644, Oct. 2014.

- [18] Murata Electronics Oy [Online]. Available: http://www.muratamems.fi

- [19] H. Danneels, K. Coddens, and G. Gielen, "A fully-digital, 0.3 V, 270 nW capacitive sensor interface without external references," in *Proc. Eur. Solid-State Circuits Conf. (ESSCIRC)*, 2011, pp. 287–290.

- [20] N. Nizza, M. Dei, F. Butti, and P. Bruschi, "A low-power interface for capacitive sensors with PWM output and intrinsic low pass characteristic," *IEEE Trans. Circuits Syst. I*, vol. 60, no. 6, pp. 1419–1431, Jun. 2013.

- [21] H. Ha, D. Sylvester, D. Blaauw, and J. Sim, "12.6 A 160 nW 63.9 fJ/conversion-step capacitance-to-digital converter for ultra-low-power wireless sensor nodes," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, 2014, pp. 220–221.

- [22] S. Oh, W. Jung, K. Yang, D. Blaauw, and D. Sylvester, "15.4b incremental sigma-delta capacitance-to-digital converter with zoom-in 9b asynchronous SAR," in *Symp. VLSI Circuits Dig. Tech. Papers*, 2014, pp. 222–223.

- [23] W. Jung, S. Jeong, S. Oh, D. Sylvester, and D. Blaauw, "A 0.7 pF-to-10 nF fully digital capacitance-to-digital converter using iterative delay-chain discharge," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, 2015, pp. 484–485.

**Sechang Oh** (S'12) received the B.S. degree in electrical engineering from Seoul National University, Seoul, Korea, in 2011, and the M.S. degree in electrical engineering from the University of Michigan, Ann Arbor, MI, USA, in 2014, where he is currently pursuing the Ph.D. degree in electrical engineering.

His research interests include low-power sensor in-

**Yoonmyung Lee** (S'08–M'12)received the B.S. degree in electronic and electrical engineering from Pohang University of Science and Technology (POSTECH), Pohang, Korea, in 2004, and the M.S. and Ph.D. degree from the University of Michigan, Ann Arbor, MI, USA, in 2008 and 2012, respectively. During his Ph.D. study, he worked at research labs with Intel Corporation and IBM, exploring novel circuit designs for low power on-die interconnect fabrics and SRAM.

From 2012 to 2015, he was with University of Michigan as research faculty. In 2015, he joined Sungkyunkwan University, Suwon, Korea, as an Assistant Professor. His research interests include energy-efficient integrated circuits design for low-power high-performance VLSI systems and millimeter-scale wireless sensor systems.

Dr. Lee has received a Samsung Scholarship and an Intel Ph.D. fellowship.

**Jingcheng Wang** (S'15) received the B.S. degree in electrical engineering from the University of Michigan, Ann Arbor, MI, USA, in 2014, where he is currently working toward the M.S. and Ph.D. degrees in electrical engineering.

He received a Dwight F. Benton Fellowship in 2015 from the University of Michigan. His research interests are in high-speed and low-power VLSI circuits and systems.

**Ziyun Li** (S'15) received the B.S. degree in electrical and computer engineering in 2014 from the University of Michigan, Ann Arbor, MI, USA, where he is currently working toward the Ph.D. degree at the Michigan Integrated Circuit Lab.

His current research interests include high-performance, low-power computer vision processing to enable UAV operations.

**Zhiyoong Foo** received the B.S., M.S., and Ph.D. degrees in electrical engineering from the University of Michigan, Ann Arbor, MI, USA.

He is currently heading CubeWorks Inc., a startup spun out of University of Michigan commercializing ultra-low-power systems. His research includes lowcost and low-power VLSI circuit systems integration.

**David Blaauw** (M'94–SM'07–F'12) received the B.S. in physics and computer science from Duke University, Durham, NC, USA, in 1986, and the Ph.D. degree in computer science from the University of Illinois, Urbana, IL, USA, in 1991.

After his studies, he worked for Motorola, Inc. in Austin, TX, USA, where he was the manager of the High Performance Design Technology group. Since August 2001, he has been on the faculty at the University of Michigan where he is a Professor. He has published over 450 papers and holds 40 patents. His

work has focused on VLSI design with particular emphasis on ultra-low-power and high-performance design.

Dr. Blaauw was the Technical Program Chair and General Chair for the International Symposium on Low Power Electronic and Design (ISLPED). He was also the Technical Program Co-Chair of the ACM/IEEE Design Automation Conference and a member of the ISSCC Technical Program Committee.

**Yejoong Kim** (S'08–M'15) received the Bachelor degree in electrical engineering from Yonsei University, South Korea, in 2008, and the Master and Ph.D. degrees from the University of Michigan, Ann Arbor, MI, USA, in 2012 and 2015, respectively, all in electrical engineering.

He is currently a Research Fellow at the University of Michigan. His research interests include subthreshold circuit designs, ultra-low-power SRAM, and the design of millimeter-scale computing systems and sensor platforms.

**Dennis Sylvester** (S'95–M'00–SM'04–F'11) received the Ph.D. degree from the University of California, Berkeley, CA, USA.

He is a Professor of electrical engineering and computer science at the University of Michigan, Ann Arbor, MI, USA. He is the Director of the Michigan Integrated Circuits Laboratory (MICL), a group of ten faculty and 70+ graduate students. He has held research staff positions in the Advanced Technology Group of Synopsys, Hewlett-Packard Laboratories, and visiting professorships at the

National University of Singapore and Nanyang Technological University. He co-founded Ambiq Micro, a fabless semiconductor company developing ultra-low-power mixed-signal solutions for compact wireless devices. He has published over 400 articles along with one book and several book chapters. His research interests include the design of millimeter-scale computing systems and energy efficient near-threshold computing. He holds 22 U.S. patents and serves as a consultant and technical advisory board member for electronic design automation and semiconductor firms in these areas.

Wanyeong Jung (S'13) received the B.S. degree in electrical engineering from Seoul National University, Korea, in 2012, and the M.S. degree in electrical engineering from the University of Michigan, Ann Arbor, MI, USA, in 2014, where he is currently pursuing the Ph.D. degree in electrical engineering.

His research interests include ultra-low power voltage regulators and sensors design for self-powered wireless sensor nodes.