# A Noise Reconfigurable All-Digital Phase-Locked Loop Using a Switched Capacitor-Based Frequency-Locked Loop and a Noise Detector

Taekwang Jang<sup>®</sup>, *Student Member, IEEE*, Seokhyeon Jeong<sup>®</sup>, *Student Member, IEEE*, Dongsuk Jeon<sup>®</sup>, Kyojin David Choo, *Student Member, IEEE*, Dennis Sylvester, *Fellow, IEEE*, and David Blaauw, *Fellow, IEEE*

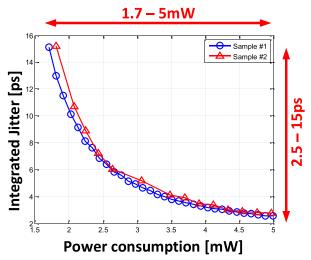

Abstract—Programmability is one of the most significant advantages of a digital phase-locked loop (PLL) compared with a charge-pump PLL. In this paper, a digital PLL that extends programmability to include noise is introduced. A digitally controlled oscillator (DCO) using a switched capacitor for frequency feedback is proposed to maintain a constant figure of merit while reconfiguring its noise performance. The proposed DCO offers an accurate and linear frequency tuning curve that is insensitive to environmental changes. A noise detection circuit using the statistical property of a bang-bang phase and frequency detector is proposed to autonomously adjust the output noise level depending on the noise specification. A prototype design is fabricated in a 28-nm FDSOI process. The integrated phase noise of the proposed PLL can be configured from 2.5 to 15 ps, while the power consumption ranges from 1.7 to 5 mW.

Index Terms—All-digital phase-locked loop (ADPLL), clock generation, linearization, noise reconfiguration, phase-locked loop (PLL), switched capacitor.

#### I. INTRODUCTION

RECENTLY, all-digital phase-locked loops (ADPLLs) have been widely adopted for their small size, configurability, and portability [1]–[3]. Although an ADPLL is less susceptible to environmental variation compared with its analog counterparts, it is still affected by process and temperature changes. This leads to overly restrictive design specifications to ensure robust performance over the entire process and temperature range, causing a power penalty. For instance, gain of a digitally controlled oscillator (DCO) and a phase detector are the dominant factors that can cause variation in the loop dynamics. When a time-to-digital converter (TDC) is used as a phase detector, its delay elements are susceptible to environmental variation, so its quantization step represented as unit delay of the TDC is variable [4]–[9]. A 1-bit TDC or bang-bang phase frequency detector (BBPFD) is usually

Manuscript received May 10, 2017; revised August 2, 2017, October 17, 2017, and November 3, 2017; accepted November 12, 2017. Date of publication December 8, 2017; date of current version December 26, 2017. This paper was approved by Guest Editor Keith Bowman. (Corresponding author: Taekwang Jang.)

- T. Jang, S. Jeong, K. D. Choo, D. Sylvester, and D. Blaauw are with the Department of Electrical and Computer Engineering, University of Michigan, Ann Arbor, MI 48109 USA (e-mail: tkjang@umich.edu).

- D. Jeon is with the Department of Convergence Science and Technology, Seoul National University, Seoul 08826, South Korea.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2017.2776313

considered to operate independently of environmental changes because it does not have a delay element. However, the output amplitude of a BBPFD is fixed as 1 and 0 regardless of the input amplitude, making the input-to-output ratio dependent solely on the input amplitude [10]–[12]. Thus its gain is dependent on the amplitude of the input signal, which comes from DCO phase noise in a digital PLL. Therefore, the need for a DCO design, which provides stable gain and noise, is emphasized in a BBPFD-based digital PLL in order to ensure robust operation under the environmental changes.

Reusability also contributes to variation in PLL operation. The increased fabrication, design, and verification costs in the latest technologies have led to a demand for reusability. Reusability also reduces the development time of a product. However, there is a classic tradeoff between productivity and efficiency. A generic PLL should cover a wide range of specifications. Thus, it cannot be optimized for any specific product and will inevitably result in wasted energy.

There are a few requirements for a generic PLL. First, a generic PLL must have a wide frequency range to make it suitable for many products. Noise optimization for both shortterm and long-term jitters is required to broaden its application space. Reconfigurability of the PLL mode is beneficial so that it can operate near an energy-optimal point in many applications. A charge-pump PLL is a well-known architecture showing robust operation. However, its analog nature creates problems such as a large loop filter size and limited reconfiguration ability in deep submicrometer technologies. For instance, digital loop filter reconfiguration is much more flexible with less area overhead compared to a charge-pump PLL using current digital-to-analog converter (DAC) and loop filter switches [8]. In addition, two-point modulation for the spread spectrum can be done easily without employing addition DAC [13]. Delta-sigma modulator (DSM) noise cancellation in a fractional-N mode is also more straightforward with high accuracy and less overhead, whereas a charge-pump PLL requires additional charge pump and pulsewidth control and suffers from mismatch [6], [14]. A multiplying delaylocked loop (MDLL) offers the advantage of reduced oscillator noise by refreshing the oscillator phase with a reference [15]. Nevertheless, its limited multiplication ratio and large period jitter at edge insertion make the MDLL an undesirable architecture for a generic PLL [16]. On the other hand, a digital PLL can provide robust operation across wide input and output frequency ranges. In addition, its digital nature helps make it small and reconfigurable in the latest technology. Therefore, a digital PLL offers an attractive architecture to meet the requirements of a generic PLL.

A DCO is considered the most important building block of a generic digital PLL for a couple reasons. First, the output phase noise is mostly governed by DCO noise, especially when a ring oscillator is used. An LC oscillator reduces the noise significantly but is difficult to adopt in a generic PLL due to the frequency range and size requirements. Noise filtering techniques have been proposed to improve the phase noise in a ring oscillator [17], [18]. However, their figure of merit (FoM) is still worse than the theoretical limit of a ring oscillator [19] due to the additional power consumption and noise generation of the frequency detection circuit. Therefore a ring oscillator structure that can operate near its theoretical limit [19] is desirable. Second, a DCO's gain and frequency range affect the performance of a PLL significantly. Nevertheless, the gain and frequency range vary significantly because its delay relies on the intrinsic parameters of the transistors. The change in the DCO gain results in variation of the PLL loop bandwidth as it moves away from the optimal point. Therefore, an accurate and linearized frequency tuning curve is required to maintain a constant loop bandwidth.

In this paper, we implemented a digital PLL with a nested frequency-locked loop (FLL) that linearizes the DCO frequency tuning curve, providing stable gain. Therefore, the loop dynamics are insensitive to environmental variations. We propose a noise reconfiguration scheme using a noise reconfigurable DCO to create a tradeoff between power and noise. We furthermore propose a noise detection circuit that uses the statistical behavior of BBPFD to self-adjust the noise depending on the noise specification.

### II. PROPOSED APPROACH

# A. Basic Concept

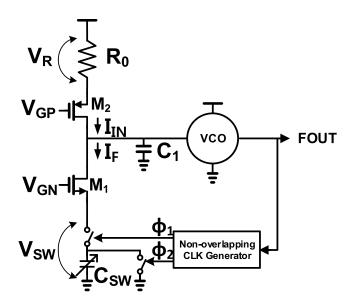

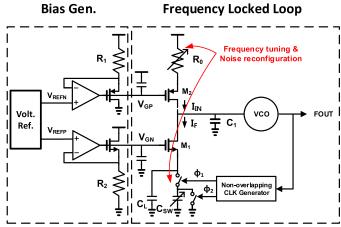

The proposed design adopts an FLL structure using a switched capacitor for the frequency feedback [20]–[26]. Its basic concept is introduced in Fig. 1. The input current  $I_{\rm IN}$  is generated by regulating a resistor  $R_0$  with the voltage  $V_R$ . The feedback current  $I_F$  is defined by the following equation:

$$I_F = C_{\rm sw} V_{\rm sw} f_{\rm out} \tag{1}$$

where  $C_{\rm sw}$ ,  $V_{\rm sw}$ , and  $f_{\rm out}$  are switching capacitance, voltage on  $C_{\rm sw}$ , and output frequency, respectively. Assuming a large gain from the frequency detection block,  $I_F$  should be equal to  $I_{\rm IN}$  in the steady state. Therefore, the output frequency can be calculated using the following equation:

$$C_{\text{sw}}V_{\text{sw}}f_{\text{out}} = \frac{V_R}{R_0}$$

$$f_{\text{out}} = \frac{V_R}{V_{\text{sw}}} \frac{1}{R_0 C_{\text{sw}}}.$$

(2)

When the identical voltage is used for  $V_R$  and  $V_{sw}$ , the oscillation frequency of the FLL is defined in the following equation:

$$f_{\text{out}} = \frac{1}{R_0 C_{\text{sw}}}. (3)$$

Fig. 1. Conceptual schematic of an FLL using a switched capacitor frequency feedback.

Therefore, the PLL loop can tune either  $R_0$  or  $C_{\rm sw}$  in order to lock the FLL frequency to the PLL target frequency.

Conventional methods of DCO implementation includes a gate voltage control of a current starving transistor [27], a series resistance control to load capacitor [28] or to supply voltage [29], a delay cell size control [30] or a digital current control for a current-controlled oscillator [31], all relying on the of physical device characteristics, and it is difficult to achieve high linearity or process, voltage, temperature (PVT) invariance [24]. In contrast, an FLL using switched capacitor can accurately control the output frequency because it is explicitly determined as (3) using a negative feedback loop [20]–[26].

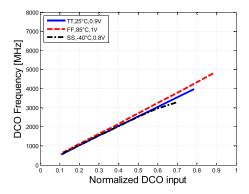

As an example, Fig. 2 shows simulated frequency tuning curves of conventional and proposed DCOs. Fig. 2(a) shows a conventional case where a DAC is attached to a current starved voltage-controlled oscillator (VCO) to form a DCO that shows a non-linear and PVT dependent frequency tuning curve. In contrast, a DCO with the proposed scheme demonstrates a highly linear and accurate tuning curve, as shown in Fig. 2(b).

# B. Loop Dynamics of the Proposed FLL

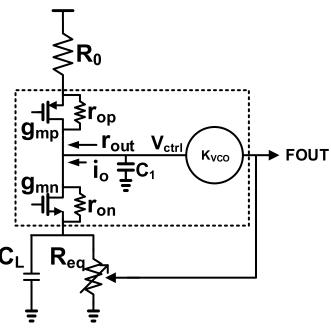

In this section, the loop dynamics of the proposed FLL are analyzed. First, the feedforward path of the FLL is from the output current generated by the frequency detection block to the output frequency of the DCO marked with a dotted line in Fig. 3. The control voltage  $v_{\rm ctrl}$  is generated by the output current  $i_o$  multiplied by the output impedance of the detection block as shown in the following equation:

$$r_{\text{out}} = (R_0 + r_{\text{op}}(1 + g_{\text{mp}}R_0)) \parallel (R_{\text{eq}} + r_{\text{on}}(1 + g_{\text{mn}}R_{\text{eq}}))$$

$$\simeq r_{\text{op}}R_0g_{\text{mp}} \parallel r_{\text{on}}R_{\text{eq}}g_{\text{mn}}$$

(4)

where  $r_{\rm op}$ ,  $r_{\rm on}$ ,  $g_{\rm mp}$ , and  $g_{\rm mn}$  are PMOS output resistance, NMOS output resistance, PMOS transconductance, and NMOS transconductance, respectively. Assuming  $r_{\rm op} = r_{\rm on} = r_o$ , and  $M_1$  and  $M_2$  are in a subthreshold region so that their transconductance is maximized to  $I_{\rm bias}/{\rm mv}_T$ ,  $r_{\rm out}$  can be

Fig. 2. Simulated frequency tuning curves. (a) With DAC attached to a VCO. (b) Proposed FLL using switched capacitor frequency feedback.

Fig. 3. Simplified schematic of the proposed FLL for the analysis of the feedforward transfer function.

simplified to  $(r_o R_0 I_{\text{bias}}/2mv_T)$  where m is  $1 + C_d/C_{\text{ox}}$  and  $C_{\text{d}}$  and  $C_{\text{ox}}$  are depletion and oxide capacitances, respectively. Then,  $v_{\text{ctrl}}$  can be found as

$$v_{\text{ctrl}} = z_{\text{out}} i_o = \frac{r_{\text{out}}}{1 + s \cdot r_{\text{out}} C_1} i_o.$$

(5)

The output frequency  $f_{\text{out}}$  can be calculated by multiplying the gain for the VCO,  $K_{\text{VCO}}$ , to (5)

$$f_{\text{out}} = \frac{K_{\text{VCO}} r_{\text{out}}}{1 + s \cdot r_{\text{out}} C_1} i_o. \tag{6}$$

Then, the feedforward transfer function from the output current of the frequency detector to the output frequency is

$$H_{ff}(s) = \frac{f_{\text{out}}}{i_o} = \frac{K_{\text{VCO}}r_{\text{out}}}{1 + s \cdot r_{\text{out}}C_1}.$$

(7)

Note that  $1/r_{out}C_1$  is the dominant pole of the FLL.

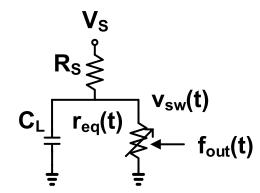

To analyze the feedback path of the proposed topology, we first need to analyze the transfer function of the switched capacitor.  $f_{\rm out}$  serves as an input to the switched capacitor, and its equivalent resistance  $r_{\rm eq}$  is the output. Then, the transfer

Fig. 4. Simplified and linearized schematic at the source of the M1 for the analysis of feedback transfer function.

function of the switched capacitor is

$$r_{\text{eq}} = \frac{\partial i_f}{\partial f_{\text{out}}} = \frac{\partial}{\partial f_{\text{out}}} \left( \frac{1}{C_{\text{sw}} f_{\text{out}}} \right) = -\frac{1}{C_{\text{sw}} f_{\text{out}}^2}.$$

(8)

The change in  $r_{\rm eq}$  results in a change in the output current of  $M_1$  by modulating its gate-to-source voltage. Fig. 4 shows the linearized circuit diagram at the source of  $M_1$ .  $R_s$  is the source resistance of  $M_1$  (shown in Fig. 1), which is expressed as  $1/g_{m1}$ .  $C_L$  is a capacitor connected in parallel to the switched capacitor to lower the ripple magnitude.  $V_s$  is a virtual source voltage that provides dc voltage on the switched capacitor.  $v_{\rm sw}'$  is the voltage on the switched capacitor, and  $v_{\rm sw}$  is the voltage on the switched capacitor excluding the sawtooth ripple caused by the switching operation. Then,  $V_s$  can be defined as

$$V_s = \left(1 + \frac{R_s}{R_{\rm eq}}\right) V_{\rm sw} \tag{9}$$

where  $V_{\rm sw}$  is the dc voltage on the switched capacitor, which is 250 mV in this design. Then,  $v_{\rm sw}$  can be found as

$$v_{\rm sw}(t) = \frac{r_{\rm eq}(t)}{R_s + r_{\rm eq}(t)} V_s. \tag{10}$$

Therefore, the transfer function from the change of  $r_{\rm eq}$  to the change of  $v_{\rm sw}$  is determined using the following equation:

$$\frac{\partial v_{\rm sw}}{\partial r_{\rm eq}} = \frac{\partial}{\partial r_{\rm eq}} \left( \frac{r_{\rm eq}(t)}{R_s + r_{\rm eq}(t)} V_s \right)_{r_{\rm eq}(t) = R_{\rm eq}} = \frac{R_s}{(R_{\rm eq} + R_s)^2} V_s. \tag{11}$$

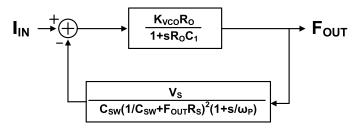

Fig. 5. Linear model of the proposed FLL.

Fig. 6. Bode plot of open-loop transfer function and closed transfer functions of the proposed FLL when  $V_s$ ,  $K_{\rm VCO}$ ,  $R_s$ ,  $f_{\rm out}$ , and  $C_{\rm SW}$  are 0.25 V, 15 GHz/V, 17  $\Omega$ , 2 GHz, and 7.5 pF, respectively.

Note that  $C_L$  is ignored for simplicity in (8). The gain from  $f_{\text{out}}$  to  $v_{\text{sw}}$  is calculated by combining (8) and (11) as shown in the following equation:

$$\frac{\partial v_{\text{sw}}}{\partial f_{\text{out}}} = \frac{\partial v_{\text{sw}}}{\partial r_{\text{eq}}} \frac{\partial r_{\text{eq}}}{\partial f_{\text{out}}} = -\frac{1}{C_{\text{sw}} f_{\text{out}}^2} \frac{R_s V_s}{(R_{\text{eq}} + R_s)^2} \frac{1}{(1 + s/\omega_{p2})}$$

$$= -\frac{R_s V_s}{C_{\text{sw}} (1/C_{\text{sw}} + f_{\text{out}} R_s)^2} \frac{1}{(1 + s/\omega_{p2})}.$$

(12)

$\omega_{p2}$  is the secondary pole generated by  $C_L$  and parallel resistance of  $R_s$  and  $R_{eq}$

$$\omega_{p2} = \frac{1}{C_L(R_s \parallel R_{eq})}. (13)$$

Finally, the feedback transfer function from  $f_{\text{out}}$  to the feedback current  $i_f$  is determined by multiplying  $-g_{m1}$  by  $v_{\text{sw}}$

$$H_{\text{fb}}(s) = -g_{m1} \frac{\partial v_{\text{sw}}}{\partial f_{\text{out}}} = \frac{V_s}{C_{\text{sw}} (1/C_{\text{sw}} + f_{\text{out}} R_s)^2 (1 + s/\omega_{p2})}.$$

(14)

The linear model of the FLL is shown in Fig. 5, and its open loop transfer function (black) is shown in Fig. 6 when  $V_s$ ,  $K_{\text{vco}}$ ,  $R_s$ ,  $f_{\text{out}}$ , and  $C_{\text{sw}}$  are 0.25 V, 15 GHz/V, 17  $\Omega$ , 2 GHz, and 7.5 pF, respectively. A wide regulation bandwidth ( $f_{\text{BW}}$ ) of more than 500 MHz is achieved.

The closed-loop gain is determined by the feedback factor using the following equation assuming a large feedforward

path gain:

$$1/H_{\rm fb}(0) = \frac{C_{\rm sw}(1/C_{\rm sw} + f_{\rm out}R_{\rm s})^2}{V_{\rm s}}[Hz/A].$$

(15)

To minimize the gain from the noise current to the output frequency,  $R_s$  must be minimized. However, given the dc bias current of  $I_{\text{bias}}$ , there is a limit to how much the transconductance can be increased, which is subthreshold transconductance,  $I_{\text{bias}}/\text{mv}_T$ . Therefore, the minimum closed-loop gain can be found as the following:

$$A_{\text{noise}} = \frac{C_{\text{sw}} (1/C_{\text{sw}} + f_{\text{out}} R_s)^2}{V_s} \frac{I_{\text{bias}}}{f_{\text{out}}}$$

$$= \frac{C_{\text{sw}} (1/C_{\text{sw}} + R_s/R_{\text{eq}} C_{\text{sw}})^2}{(1 + R_s/R_{\text{eq}})V_{\text{sw}}} \frac{I_{\text{bias}}}{f_{\text{out}}} \qquad (16)$$

$$= \frac{(1 + R_s/R_{\text{eq}})^2}{(1 + R_s/R_{\text{eq}})C_{\text{sw}} V_{\text{sw}}} \frac{I_{\text{bias}}}{f_{\text{out}}} = 1 + \frac{R_s}{R_{\text{eq}}}$$

$$A_{\text{noise,min}} = 1 + \frac{\text{mv}_T/I_{\text{bias}}}{1/f_{\text{out}} C_{\text{sw}}} = 1 + \frac{\text{mv}_T}{V_{\text{sw}}}. \qquad (17)$$

It can be seen that a large  $V_{\rm sw}$  results in reduced noise gain; however, it also reduces the control voltage range. Therefore, a tradeoff is made in the proposed design to set  $V_{\rm sw}$  to ten times  $v_T$ , allowing a 10% increase in noise gain while maintaining 400-mV control voltage range with 1-V supply. A bode plot of the closed-loop transfer function from the current input to the frequency output is displayed in Fig. 6. The noise generated by the detection circuits, primarily due to the switched capacitor and biasing resistor, is low-pass filtered at the loop bandwidth.

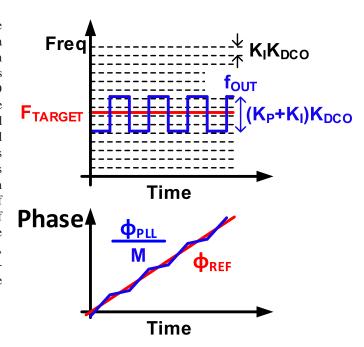

# C. Linearized Loop Dynamics of the PLL

The linearized loop dynamics of the proposed PLL follows the conventional formula [11], [12], [32], [33] except for the parasitic nondominant pole added by the FLL:

$$H_{\text{OLG}}(s) = \frac{T_{\text{REF}} K_{\text{PD}} K_{\text{DCO}} K_P}{s \cdot M} \left( 1 + \frac{\omega_z}{s} \right) \frac{1}{1 + s/\omega_{\text{FLL}}}$$

(18)

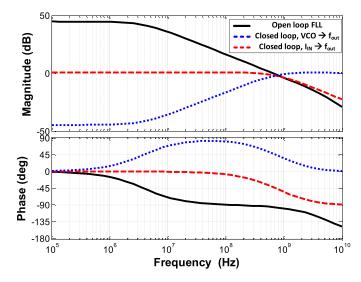

where  $K_{\rm PD}=G/\sqrt{2\pi\sigma_{\rm PLL}^2}$  [11],  $\omega_z=K_I/(K_PT_{\rm REF})$ , and  $\sigma_{\rm PLL}$  is the PLL output jitter. G is 1 when the PLL limit cycle dominates  $\sigma_{PLL}$  and 2 when DCO noise dominates  $\sigma_{\rm PLL}$  [11]. M and  $T_{\rm REF}$  are the frequency multiplication ratio and the period of reference clock, respectively. Note that (18) is equal to [32, eq. (7)] with the DCO period gain  $k_T$  replaced using the DCO frequency gain,  $K_{\text{DCO}}$  ( $k_T = K_{\text{DCO}} T_{\text{RFF}}^2 / M^2$ ). Another important observation on  $K_{DCO}$  is that it is half of the frequency change  $\Delta f_P$  caused by proportional path control. It is because +1 and -1 outputs of BBPFD corresponds to the DCO frequency change of  $+\Delta f_P/2$  and  $-\Delta f_P/2$  making effective frequency gain of DCO be  $\Delta f_P/2$ .  $1/(1+s/\omega_{\rm FLL})$ is the parasitic pole generated by the FLL, and  $\omega_{\rm FLL}$  can be approximated to  $2\pi f_{BW}$ . Note that the closed-loop transfer function of the FLL is simplified to a first-order system in (18). As  $f_{BW}$  is order-of-magnitude higher compared to the unit gain frequency of  $H_{OLG}(s)$ , the effect of this parasitic pole is negligible. In Fig. 7, open-loop transfer function of the proposed PLL is depicted when  $T_{REF}$ ,  $K_{PD}$ ,  $K_{DCO}$ ,  $K_P$ , M,

Fig. 7. Open-loop transfer function of the proposed PLL.

Fig. 8. Simulated phase noise curves of the free running VCO (red line) and the proposed FLL (blue curve).

$\omega_z$ , and  $\omega_{FLL}$  are 20 n, 6.7 × 10<sup>10</sup>, 650 k, 1, 40, 390 k, and 3.1 G, respectively. It can be seen that the effect of  $\omega_{FLL}$  is negligible in the PLL loop dynamics.

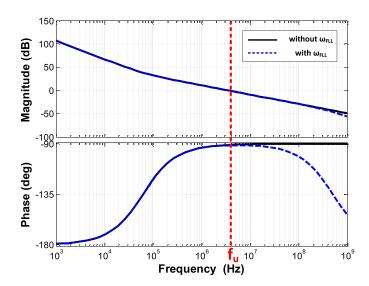

### III. NOISE ANALYSIS

One of the merits of the proposed architecture is that the output noise of the FLL is mostly determined by the frequency detection circuit. The VCO noise is high-pass filtered at the FLL bandwidth so that the noise becomes negligible when calculating the integrated phase noise, as shown in the closed-loop transfer function from the VCO noise to  $f_{\text{out}}$  [see Fig. 6 (blue dotted line]. The noise generated by the detection circuit dominates the output noise across most of the frequency range because  $f_{\text{BW}}$  is large. Phase noise simulation results of the proposed FLL (blue line) and a free funning VCO (red line) are shown in Fig. 8. The VCO noise is high-pass filtered at the FLL bandwidth (208 MHz), and the lower frequency noise is dominated by the detection circuits.

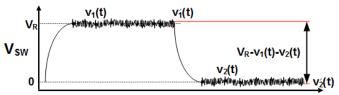

To calculate the noise property of the detection circuit, we first need to analyze the current noise generated by the switched capacitor. Fig. 9 shows the transient waveform at the top node of  $C_{\rm sw}$ ,  $V_c$ . The sampling operation happens twice per  $f_{\rm out}$  cycle, once for charging it to  $V_{\rm sw}$  and once for

Fig. 9. Transient waveform at the top node of  $C_{sw}$ .

Fig. 10. Current division branches in the frequency detection block.

discharging it to ground. In each sampling process, kT/C noise with bandwidth  $1/2 f_{\text{out}}$  is generated, so its power spectral density can be written as

$$S_{v1}(f) = S_{v2}(f) = \frac{2kT}{C_{sw}f_{out}}$$

(19)

where  $v_1$  and  $v_2$  are the sampled voltages at  $V_c$ . The amount of charge injected at every switching cycle to  $V_{\rm sw}$  can be written as  $C_{\rm sw}(v_1(t)-v_2(t))$ , so the noise current of the switched capacitor can be calculated using the following equation:

$$i_1(t) = C_{sw} f_{out}(v_1(t) - v_2(t)).$$

(20)

As  $v_1$  and  $v_2$  are uncorrelated, the power spectral density of the switched capacitor noise can be written as the following equation:

$$\overline{i_1^2} = 4kT f_{\text{out}} C_{\text{sw}} = 4kT \frac{1}{R_{\text{eq}}}.$$

(21)

Note that the noise generated by the switched capacitor is equal to the noise of a physical resistor, whose size is equal to  $R_{\text{eq}}$ .

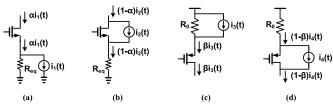

Then, we need to analyze the current division branches at the sources of  $M_1$  and  $M_2$ . First, the current division ratio at the source of  $M_1$  is analyzed in Fig. 10. The equivalent current noise from the switched capacitor  $i_1(t)$  is divided by the impedance ratio of  $R_{\rm eq}$  and  $R_s$

$$i_{\text{out},1} = \frac{R_{\text{eq}}}{R_{\text{eq}} + R_s} i_1 = \alpha i_1 = \frac{1}{A_{\text{noise}}} i_1$$

(22)

where  $i_{\text{out},1}$  is the amount of current produced at the output of the detection circuit. As mentioned in Section II, it is advantageous to increase the size of  $M_1$  to reduce the noise gain. The current division ratio  $\alpha$  is simply

$$\alpha = \frac{\frac{V_{\text{sw}}}{I_{\text{bias}}}}{\frac{V_{\text{sw}}}{I_{\text{bias}}} + \frac{mv_T}{I_{\text{bias}}}} = \frac{V_{\text{sw}}}{V_{\text{sw}} + mv_T}.$$

(23)

On the other hand,  $i_2$ , the noise generated by  $M_1$ , is highly degenerated by the source resistance  $M_1$ , and only a small

Fig. 11. Schematic of the proposed FLL with the noise sources.

fraction of i2 is delivered to the output, as described by the following equation:

$$i_{\text{out},2} = (1 - \alpha)i_2.$$

(24)

Similarly, the current noise from  $R_0$  and  $M_2$  can be calculated, as described the following equations:

$$i_{\text{out},3} = \beta i_3 \tag{25}$$

$$i_{\text{out},4} = (1 - \beta)i_4$$

(26)

where  $\beta$  is the current division ratio at the source of  $M_2$ , which is defined as the following equation when  $M_2$  is biased in a subthreshold region:

$$\beta = \frac{V_R}{V_P + m v_T}. (27)$$

Fig. 11 shows equivalent noise sources in the detection circuit,  $i_{1-4}(t)$ . The output frequency noise can be calculated by multiplying the closed-loop gain from the output current of the detection block to the output frequency. The noise contributions from  $C_{\rm sw}$ ,  $R_0$ ,  $M_1$ , and  $M_2$  can be found as follows:

$$L_{C_{\text{sw}}}(f) = \frac{4kT}{I_{\text{higs}}V_{\text{sw}}} \frac{f_{\text{out}}^2}{f^2}$$

(28)

$$L_{M_1}(f) = \left(\frac{1-\alpha}{\alpha}\right)^2 \frac{4kT\gamma_n g_{m1}}{I_{\text{bias}}^2} \frac{f_{\text{out}}^2}{f^2}$$

(29)

$$L_{R_0}(f) = \frac{\beta^2}{\alpha^2} \frac{4kT}{I_{\text{bias}} V_R} \frac{f_{\text{out}}^2}{f^2}$$

(30)

$$L_{M_2}(f) = \left(\frac{1-\beta}{\alpha}\right)^2 \frac{4kT\gamma_p g_{m1}}{I_{\text{bias}}^2} \frac{f_{\text{out}}^2}{f^2}.$$

(31)

Note that the noise from  $M_1$  and  $M_2$  are relatively negligible compared with the noise from  $C_{\rm sw}$  and  $R_0$  because  $\alpha$  and  $\beta$  are close to 1. By rewriting  $\alpha$  and  $\beta$  in (28)–(31) using (23) and (27) and by summing all of the noise sources, the overall phase noise can be found as follows:

$$L(f) = \frac{4kT}{I_{\text{bias}}} \left( \frac{1}{V_{\text{sw}}} \left( 1 + \frac{\gamma_n \text{mv}_T}{V_{\text{sw}}} \right) + A_{\text{noise}}^2 \frac{V_R + \gamma_p \text{mv}_T}{(V_R + \text{mv}_T)^2} \right) \frac{f_{\text{out}}^2}{f^2}.$$

(32)

Detailed derivation on the phase noise is described in Appendixes A and B. The discussion to this point shows that the output noise improves with a larger  $V_{\rm sw}$ .  $A_{\rm noise}$  is

a function of  $V_{\rm sw}$  as well, so increasing  $V_{\rm sw}$  helps lower the noise not only from  $M_1$  and  $C_{sw}$  but also from  $M_2$  and  $R_0$ . The smaller overdrive voltage of  $M_1$  helps reduce the noise generated by  $M_1$ . Therefore, it is advantageous to maximize the transconductance of  $M_1$  by increasing the width until  $M_1$ operates in the subthreshold region. The latter part of (32) and (B5) show that increasing both  $V_R$  and  $V_{ov,m2}$  helps reduce the output noise generated by  $M_1$  and  $R_0$ . However, increasing  $V_R$  and  $V_{ov,m2}$  limits the voltage tuning range of the VCO. As increasing  $V_R$  is almost twofold more effective than increasing  $V_{\text{ov},m2}$ , the size of  $M_2$  should be again maximized until  $M_2$  operates in the subthreshold region given a fixed voltage allocation of  $V_R$  and  $V_{ov,m2}$  combined. Note that the overall phase noise has  $I_{\text{bias}}$  in the denominator, so the DCO noise can be reconfigured by tuning the bias current while keeping the bias conditions,  $V_{sw}$ ,  $V_r$ ,  $V_{ov,m1}$ , and  $V_{mv,m2}$ constant. For instance, the FLL is configured in a low-noise mode with high current to prioritize noise performance. On the other hand, when power consumption is more important, the FLL is configured in a low-current mode, sacrificing its noise performance.

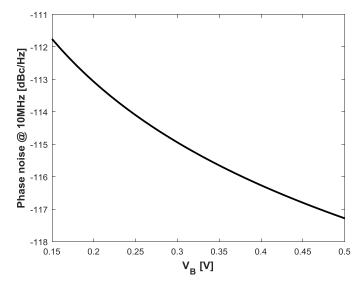

In an attempt to find an optimal biasing condition on  $C_{\rm sw}$ ,  $R_0$ ,  $M_1$ , and  $M_2$ , the conclusion thus far is to set  $M_1$  and  $M_2$  at subthreshold mode and maximize  $V_{\rm sw}$  and  $V_R$ . Here, we will discuss a strategy in deciding the optimal ratio between  $V_{\rm sw}$  and  $V_R$ . First, the voltage assigned to them is defined as  $V_B$  as follows:

$$V_B = V_{\text{sw}} + V_R = V_{\text{DD}} - V_{c,\text{range}} - 4v_T \tag{33}$$

where  $V_{c,\text{range}}$  is the input voltage range of the VCO to generate the target frequency under the PVT variation.  $4v_T$  is subtracted from  $V_{\text{DD}}$  as well to give sufficient  $V_{\text{ds}}$  to either  $M_1$  or  $M_2$ . Then, (32) can be rewritten as the following by substituting  $V_R$  with  $V_B - V_{\text{sw}}$ :

$$L(f) = \frac{4kT}{I_{\text{bias}}} \left( \frac{1}{V_{\text{sw}}} \left( 1 + \frac{\gamma_n m v_T}{V_{\text{sw}}} \right) + \left( 1 + \frac{m v_T}{V_{\text{sw}}} \right)^2 \frac{V_B - V_{\text{sw}} + \gamma_p m v_T}{(V_B - V_{\text{sw}} + m v_T)^2} \right) \frac{f_{\text{out}}^2}{f^2}.$$

(34)

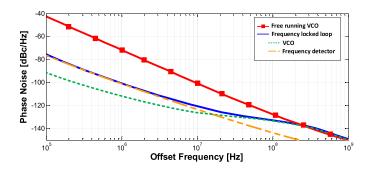

The phase noise at 10-MHz offset is shown in Fig. 12 when T,  $I_{\text{bias}}$ ,  $\gamma_n$ ,  $\gamma_p$ ,  $v_T$ , m, and  $f_{\text{out}}$  are 300 °C, 3 mA, 2/3, 2/3, 2/6 mV, 1.2, and 2 GHz, respectively. The optimal noise performance is achieved when  $V_R$  is almost equal to  $V_{\text{sw}}$ . The numerical solutions  $V_{\text{sw}} = 0.271$  and  $V_R = 0.229$  are found when  $V_B = 0.5$  after differentiating (34) and setting it equal to 0. Note that  $V_{\text{sw}}$  is weighted slightly more than  $V_R$  because  $A_{\text{noise}}$  affects both the noise from  $C_{\text{sw}}$  and  $V_R$ .

Equation (34) can be simplified assuming equal  $V_R$  and  $V_{sw}$  to intuitively understand its theoretical limit in terms of its FoM

$$L_{\text{opt}}(f) \simeq \frac{4k\text{T}}{I_{\text{bias}}} \left( \frac{1}{V_{\text{sw}}} \left( 1 + \frac{\gamma_n \text{mv}_T}{V_{\text{sw}}} \right) + \frac{1}{V_R} \left( 1 + \frac{\gamma_p \text{mv}_T}{V_R} \right) \right) \frac{f_{\text{out}}^2}{f^2}$$

$$= \frac{8k\text{T}}{I_{\text{bias}} V_{\text{sw}}} \left( 1 + \frac{\gamma_n \text{mv}_T}{V_{\text{sw}}} \right) \frac{f_{\text{out}}^2}{f^2}. \tag{35}$$

Fig. 12. Phase noise at 10-MHz offset according to (4) when T,  $I_{\rm bias}$ ,  $\gamma_n$ ,  $\gamma_p$ ,  $v_T$ , and  $f_{\rm out}$  are 300 °C, 3 mA, 2/3, 2/3, 26 mV, and 2 GHz, respectively.

Finally, the FoM of the proposed oscillator at its optimal biasing state can be found as the following:

FoM =

$$10 \log \frac{8kT}{I_{\text{bias}}V_{\text{sw}}} \left( 1 + \frac{\gamma_n \text{mv}_T}{V_{\text{sw}}} \right) \frac{f_{\text{out}}^2}{f^2} \times \frac{I_{\text{bias}}V_{\text{DD}}}{1 \text{ mW}} \times \frac{f^2}{f_{\text{out}}^2}$$

$$= 10 \log \frac{8kTV_{\text{DD}}}{10^{-3}V_{\text{sw}}} \left( 1 + \frac{\gamma_n \text{mv}_T}{V_{\text{sw}}} \right). \tag{36}$$

The first observation regarding (36) is that the FoM of the proposed oscillator only depends on the voltage ratio of  $V_{\rm DD}$  and  $V_{\rm sw}$ , assuming  $V_{\rm SW} \gg \gamma_n v_T$ . The theoretical FoM maximum is found when  $V_{\rm sw} = V_{\rm DD}/2$ , in which case  $V_B = V_{\rm DD}$ , allowing zero voltage for  $V_{c,\rm range}$ ,  $M_1$ , and  $M_2$ . It is also assumed that  $\gamma_n v_T/V_{\rm sw} \ll 1$

$$FoM_{min} = 10 \log \frac{8kTV_{DD}}{10^{-3}V_{DD}/2} = 10 \log \frac{16kT}{10^{-3}} \approx -161.79.$$

(37)

As an example of a practical case, when  $V_{\rm DD}=1$ ,  $V_{\rm sw}=V_R=0.25$ , and there is 10% additional power consumption in the VCO and non-overlapping clock generation, the FoM of the proposed oscillator is -158.1 dBc/Hz. As a comparison, the theoretical FoM limit of a CMOS ring oscillator analyzed in [19] is determined as the following:

FoM<sub>min,ring</sub> =

$$10 \log \frac{7.33 \text{kT}}{10^{-3}} \approx -165.2.$$

(38)

The theoretical limit of the proposed oscillator is approximately 3.3 dB worse than that of a conventional ring oscillator. However, there are several other factors that need to be considered.

While adding transistors to give frequency tunability to a CMOS ring oscillator, the FoM typically gets worse. On the other hand, frequency tuning of the proposed oscillator can be achieved without FoM penalty. Therefore, the minimum FoM of a conventional ring oscillator is more over-estimated than that of the proposed oscillator.

Fig. 13. Block diagram of the proposed digitally controlled oscillator.

- 2) The frequency tuning curve of the proposed oscillator is less sensitive to environmental change as it relies on an *RC* time constant rather than the transistor speed.

- The proposed oscillator offers a highly linear frequency tuning curve, which is advantageous in the reduction of PLL loop bandwidth variation and two-point modulation [24].

- 4) The proposed oscillator offers noise reconfiguration capability by programming its bias current.

Therefore, the proposed oscillator is more efficient than a conventional ring oscillator in many applications.

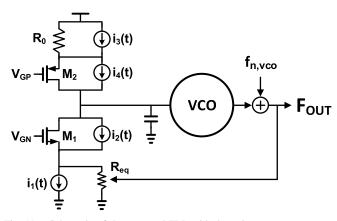

#### IV. CIRCUIT IMPLEMENTATION

A schematic of the proposed circuit is shown in Fig. 13. The gate voltages of  $M_1$  and  $M_2$  are generated using replica cells of the ones in the main branch. The amplifiers are designed to consume 500 nW so that the noise generated by those two amplifiers resides only in a very low-frequency range and is filtered by the PLL loop. Low-power voltage references are implemented using the 2-T structure proposed in [34].  $R_0$  and  $C_{\rm SW}$  are used to tune the output frequency and the noise. The size of  $M_1$  and  $M_2$  are tuned together with  $R_0$  and  $C_{\rm SW}$  so the voltages on  $R_0$  and  $C_{\rm SW}$  do not change depending on their values.

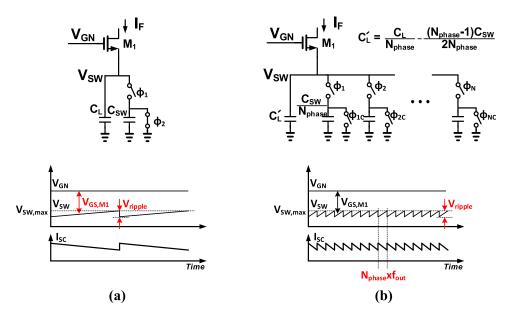

#### A. Multi-Phase Feedback

$C_L$  is placed in parallel with  $C_{\rm sw}$  to minimize the voltage ripple caused by the switching operation. When the switched capacitor is grounded, and only  $C_L$  is connected to the source of  $M_1$ ,  $V_{\rm sw}$  increases by the bias current, reducing the gate to the source voltage of  $M_1$  as shown in Fig. 14(a). Then,  $C_{\rm SW}$  is connected to the source of  $M_1$ , causing an abrupt drop at the source voltage. The ripple magnitude is determined by the ratio between  $C_L$  and  $C_{\rm SW}$ . If a small  $C_L$  is used, the voltage ripple becomes large, modulating  $V_{\rm GS}$  of  $M_1$  substantially. As  $M_1$  provides a non-linear relationship between its  $V_{\rm gs}$  and  $I_{\rm ds}$ , such fluctuation can perturb the linearity of the DCO frequency tuning curve. Therefore,  $C_L$  must be at least  $10\times$  greater than  $C_{\rm sw}$  to sufficiently lower the ripple

Fig. 14. Voltage ripple caused by the switching operation. (a) When a single phase is used. (b) When multi-phases are used.

magnitude. However, a large  $C_L$  incurs low second pole frequency in the FLL, degrading the stability, and causing area penalty. In this paper, we adopted multi-phase feedback from the VCO so that its effective switching frequency becomes  $N_{\rm phase}$  times higher, where  $N_{\rm phase}$  is the number of VCO phases as shown in Fig. 14(b). Then, the total capacitance connected in parallel with the switching capacitance is reduced by the factor  $N_{\text{phase}}$ , and it helps to provide higher  $f_{\text{BW}}$  and phase margin. In addition, the multi-phase feedback helps to greatly reduce the area. As the switching capacitance is reduced by the factor  $N_{\rm phase}$ , the total parallel capacitance can also be reduced by the same fator. Furthermore, nearly half of the non-switching capacitors are connected to the source of  $M_1$ , serving as parallel capacitors. Therefore, the size of the additional capacitance is  $C_L/N_{\text{phase}} - (N_{\text{phase}} - 1)C_{\text{sw}}/2N_{\text{phase}}$ , which is approximately 5 pF, while the total switching capacitance is 7.5 pF. Compared with 75 pF, when single-phase feedback is used, 93% of the area is saved.

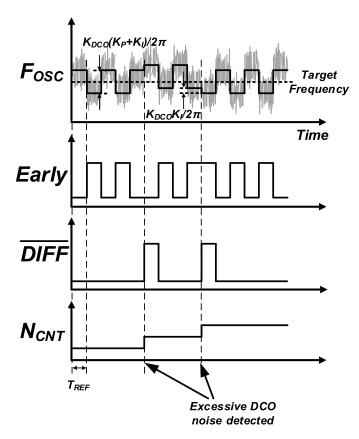

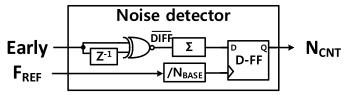

#### B. Noise Detector

In this section, a noise detector circuit using the statistical behavior of the BBPFD output is demonstrated. A digital PLL using a BBPFD has a limit cycle due to the non-linearity of the BBPFD. Assuming no DCO noise is present, the DCO control alternates between two numbers neighboring the target frequency at every reference cycle. The BBPFD output also alternates between 1 and 0, and the resulting feedback phase is shown in Fig. 15. The VCO phase drawn in a blue color follows the reference phase. The peak difference between the feedback and reference phase is the magnitude of the limit cycle,  $\Phi_{lmt}$ . It can be found as the following equation where  $K_{DCO}$  is the DCO gain,  $K_P$  is the proportional path gain, and  $K_I$  is the integral path gain:

$$\Phi_{\rm lmt} = \frac{2\pi K_{\rm DCO}(K_P + K_I)T_{\rm REF}}{M}.$$

(39)

Fig. 15. Behavior of BBPFD-based digital PLL when DCO noise is not present.

When DCO noise presents, it perturbs the DCO output phase, and its magnitude may exceed  $\Phi_{lmt}/2$ . In such cases, BBPFD produces consecutive 1 or 0 s. In Fig. 16, early is the output of the BBPFD. At times  $t_1$  and  $t_2$ , BBPFD generates either consecutive 1 or 0 s due to the excessive noise of the DCO.

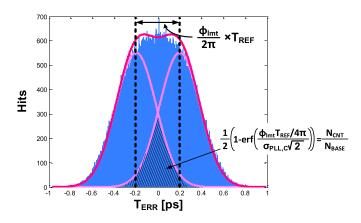

The histogram of the feedback phase is shown in Fig. 17. The DCO phase noise produces a Gaussian distribution in the feedback phase, and the limit cycle offsets the distribution by  $\pm \Phi_{lmt}/2$ . The shaded region represents the possibility that the accumulated DCO noise exceeds  $\Phi_{lmt}/2$ , in which case the BBPFD produces either consecutive 1 or 0 s.  $\sigma_{PLL,C}$  is the

Fig. 16. Transient waveforms (drawn from simulation results) of output frequency ( $f_{out}$ ), PFD output (early), and the noise detection result (DIFF).

Fig. 17. Simulated histogram of the feedback time error.

continuous random part of the PLL output noise which will be explained at the end of this Section IV-B. A schematic to detect such an event is shown in Fig. 18. The BBPFD output is compared with its previous value, and when they are the same, the noise count is increased by 1. After  $N_{\rm BASE}$  cycles of  $F_{\rm REF}$ , the noise count  $N_{\rm CNT}$  is delivered to the DCO control block.  $f_{\rm out}$  is inversely proportional to the switching capacitance as shown in (3). Therefore,  $K_{\rm DCO}$  can be accurately determined as a capacitance ratio between total switching capacitance,  $C_{\rm SW}$  and unit capacitance,  $f_{\rm out}C_u/C_{\rm sw}$ , assuring robust operation of the noise detector. As the DCO noise is adjusted using the proposed noise detector and the

Fig. 18. Proposed noise detection circuit.

Fig. 19. Simulated PLL output noise as a function of DCO noise.

DCO gain is accurately controlled using a capacitor ratio, the PLL loop dynamics stay largely invariant to environmental changes.

In this part, the PLL bandwidth and output jitter will be derived in terms of the DCO noise and other PLL configuration parameters. The unity gain frequency of the open-loop transfer function of the PLL  $f_u$  can be found by equalizing the absolute value of (18) to 1 and it is

$$f_u = \frac{1}{2\pi} \frac{T_{\text{REF}} K_{\text{PD}} K_{\text{DCO}} K_P}{M} = \frac{1}{2\pi} \frac{T_{\text{REF}} K_{\text{DCO}} K_P}{M} \frac{G}{\sqrt{2\pi} \sigma_{\text{PLL}}}.$$

(40)

$\sigma_{PLL}$  is composed of three major elements of the integrated DCO noise ( $\sigma_{PLL,DCO}$ ), the random noise caused by a random walk of BBPFD input phase ( $\sigma_{PLL,rw}$ ), and the limit cycle ( $\sigma_{PLL,lmt}$ ). First of all,  $\sigma_{PLL,lmt}$  can easily be calculated by assuming a noiseless DCO as shown in Fig. 15. As the feedback phase alternates  $\pm \Phi_{lmt}/2$ , the PLL jitter can be found as

$$\sigma_{\rm PLL,lmt} = \frac{\Phi_{\rm lmt} T_{\rm REF}}{4\pi} \simeq \frac{K_{\rm DCO} K_P T_{\rm REF}^2}{2M}.$$

(41)

Assuming there exists a very small DCO noise compared to  $\sigma_{PLL,lmt}$ , the input jitter of BBPFD random walks from  $-\Phi_{lmt}/2$  to  $+\Phi_{lmt}/2$ . This noise can be assumed to follows a uniform distribution [10], so that  $\sigma_{PLL,rw}$  is:

$$\sigma_{\text{PLL,rw}} = \frac{K_{\text{DCO}} K_P T_{\text{REF}}^2}{\sqrt{12} M}.$$

(42)

Fig. 20. Detailed schematic of the proposed digital PLL.

Note that standard deviation of the noise injected from the limit cycle behavior and the random walk is  $(\sigma_{PLL,lmt}^2 + \sigma_{PLL,rw}^2)^{1/2} = K_{DCO}K_PT_{REF}^2/\sqrt{3}~M$  which is equal to [32, eq. (12)].

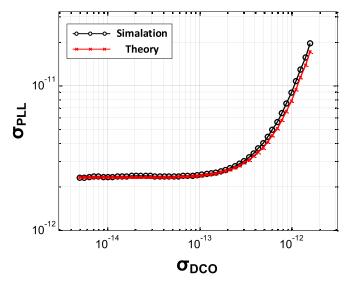

Assuming that the DCO noise is dominant at the output of the PLL and its flicker noise is negligible compared to the white noise, the PLL output noise induced by DCO,  $\sigma_{\text{PLL,DCO}}$  can be approximated as a function of  $\sigma_{\text{DCO}}$  and  $f_u$  as the following [32]:

$$\sigma_{\rm PLL,DCO} = \sigma_{\rm DCO} \sqrt{\frac{f_{\rm out}}{4\pi f_u}} = \sigma_{\rm DCO} \sqrt{\frac{M}{4\pi f_u T_{\rm REF}}}.$$

(43)

Assuming  $\sigma_{PLL,DCO}$  is dominant compared to  $\sigma_{PLL,lmt}$  and  $\sigma_{PLL,rw}$ ,  $\sigma_{PLL}$  in (40) can be replaced with  $\sigma_{PLL,DCO}$  in (42) and  $\sigma_{PLL,DCO}$  can be found as

$$\sigma_{\rm PLL,DCO} = \sigma_{\rm DCO}^2 \frac{\sqrt{\pi} M^2}{\sqrt{2} T_{\rm REF}^2 K_{\rm DCO} K_P G}.$$

(44)

Note that  $\sigma_{PLL,DCO}$  is proportional to the square of the DCO noise because it exacerbates  $\sigma_{PLL,DCO}$  by reducing the phase detector gain as well as by its own power. The total continuous random noise without the limit cycle is

$$\sigma_{\text{PLL},C} = \sqrt{\sigma_{\text{PLL},DCO}^2 + \sigma_{\text{PLL},rw}^2} \\

= \sqrt{\left(\sigma_{\text{DCO}}^2 \frac{\sqrt{\pi} M^2}{\sqrt{2} T_{\text{REF}}^2 K_{\text{DCO}} K_P G}\right)^2 + \left(\frac{K_P K_{\text{DCO}} T_{\text{REF}}^2}{\sqrt{12} M}\right)^2}.$$

(45)

The distribution of the total continuous random noise is shifted by  $\pm \sigma_{PLL,lmt}$  depending on the BBPFD output. Therefore,

the output jitter of the PLL can be found as the following:

$$\sigma_{\text{PLL}} = \sqrt{\sigma_{\text{PLL},C}^2 + \sigma_{PLL,lmt}^2}$$

$$= \sqrt{\left(\sigma_{\text{DCO}}^2 \frac{\sqrt{\pi} M^2}{\sqrt{2} T_{\text{REF}}^2 K_{\text{DCO}} K_P G}\right)^2 + \left(\frac{K_P K_{\text{DCO}} T_{\text{REF}}^2}{\sqrt{3} M}\right)^2}.$$

(46)

Equation (46) is compared with a behavioral simulation result in Fig. 19 when  $T_{REF}$ ,  $K_{DCO}$ , M, and  $K_P$  are 20 n, 400 k, 50, and 1, respectively.

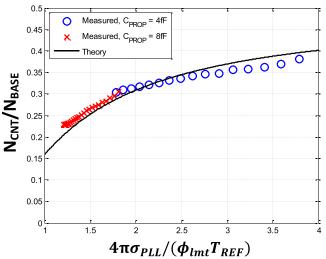

In this paper, we found that the resulting distribution of the continuous random noise can be approximated as a Gaussian distribution when the integrated DCO noise is dominant compared to  $\sigma_{PLL,rw}$ . Assuming an accurate noise adjustment,  $\sigma_{PLL,C}$  can be derived from the equation shown in Fig. 17

$$\sigma_{\text{PLL},C} = \frac{\Phi_{\text{lmt}} T_{\text{REF}} / 4\pi}{\sqrt{2} \cdot \text{erf}^{-1} \left( 1 - \frac{2N_{\text{CNT}}}{N_{\text{BASE}}} \right)} \simeq \frac{K_{\text{DCO}} K_P T_{\text{REF}}^2}{2\sqrt{2} M \cdot \text{erf}^{-1} \left( 1 - \frac{2N_{\text{CNT}}}{N_{\text{BASE}}} \right)}.$$

(47)

Finally,  $f_u$  and  $\sigma_{PLL}$  can be expressed as the following equations which are independent to the environmental changes. Note that  $K_{DCO}$  is replaced to  $(M/T_{REF}) \times (C_u/C_{SW})$

$$\sigma_{\text{PLL},C} = \frac{K_P T_{\text{REF}}(C_u/C_{\text{SW}})}{2\sqrt{2}\text{erf}^{-1} \left(1 - \frac{2N_{\text{CNT}}}{N_{\text{BASE}}}\right)}$$

$$f_u = \frac{1}{2\pi} \frac{T_{\text{REF}} K_{\text{DCO}} K_P}{M} \frac{G}{\sqrt{2\pi} \sigma_{\text{PLL}}} = \frac{G \cdot \text{erf}^{-1} \left(1 - \frac{2N_{\text{CNT}}}{N_{\text{BASE}}}\right)}{\pi \sqrt{\pi} T_{\text{REF}}}.$$

(49)

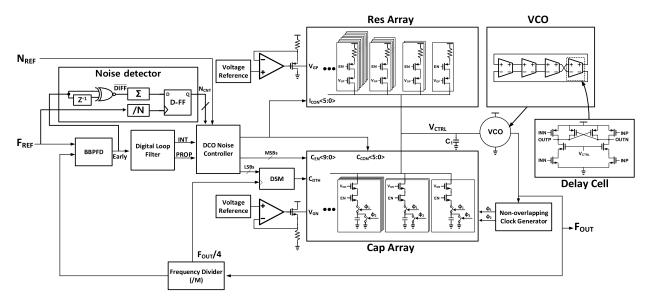

# C. Overall Implementation

Fig. 20 shows a block diagram of the proposed BBPFD-based digital PLL with PI control. A DCO noise controller tunes  $R_0$  and  $C_{SW}$  values while keeping their products constant

Fig. 21. Transient waveform (drawn from simulation results) of the proposed PLL.

at a value dependent on  $N_{\rm CNT}/N_{\rm BASE}$ , forming a noise self-adjustment loop. Note that  $I_{\rm bias}$  is inversely proportional to  $R_0$  as shown in (1) and (2), and the DCO noise is also inversely proportional to  $I_{\rm bias}$  as shown in (32). DCO frequency tuning is achieved by controlling  $C_{\rm sw}$ . The capacitance in an integral path consists of 6-bit coarse input, 10-bit fine input, and 1-bit dithering input. The proportional path is designed with 5-bit control to maintain constant DCO gain while reconfiguring  $C_{\rm sw}$ .

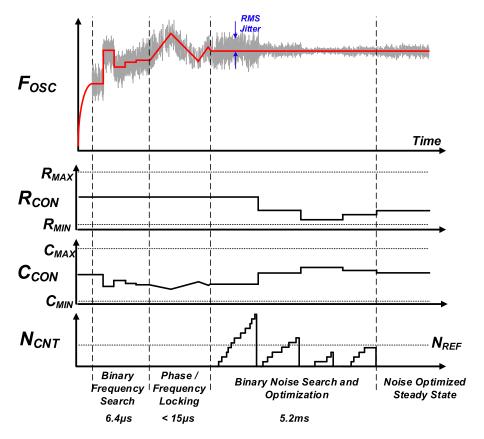

Fig. 21 shows a transient waveform of the proposed PLL. Initially, an automatic frequency control operates to find the switching capacitance that generates the target frequency. Then, the PLL loop is enabled to lock the output phase again using  $C_{\rm con}$ . After phase lock is achieved, a binary noise search is enabled using the noise detection block. Overall phase locking is achieved within 10  $\mu$ s, and the noise locking takes 5.2 ms with 50-MHz reference clock.

# V. MEASUREMENT RESULT

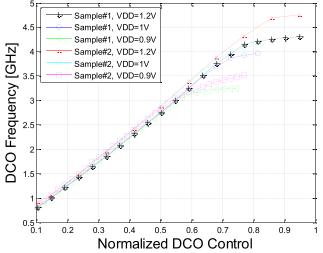

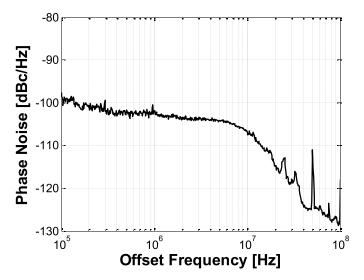

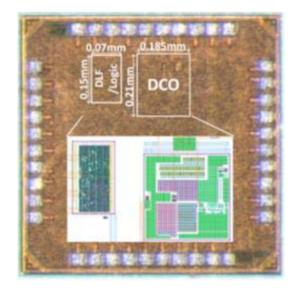

The proposed design is fabricated in a 28-nm FDSOI process. The overall area is 0.045 mm<sup>2</sup>. The proposed PLL is tested with 50-MHz input frequency generated using a function generator (Keysight33600A), and its output noise is measured using a spectrum analyzer (Agilent N9030A). Frequency tuning curves of the proposed FLL are measured in Fig. 22. It show highly linear frequency tuning curve until the VCO tuning range is limited by the supply headroom. Fig. 23 shows the power consumption of the PLL and the

Fig. 22. Measured DCO frequency tuning curve.

integrated phase noise. The integrated output phase noise is inversely proportional to the power consumption, as expected in (32). The integrated jitter can be configured from 2.5 to 15 ps while making a tradeoff with the power consumption from 1.7 to 5 mW. Fig. 24 illustrates the function of the noise detection circuit depending on the configuration of the PLL.  $K_{\rm DCO}K_P$  is changed from 600 kHz/LSB to 4 MHz/LSB and  $K_{\rm DCO}K_I$  is adjusted in accordance with  $K_P$  keeping  $K_P/K_I$  as 128 assuring the PLL loop stability. The noise count shows a monotone relationship between the DCO noise amount and the noise count enabling the stable operation.

Fig. 23. Measurement results of the integrated phase noise and the power consumption depending on the jitter configuration.

Fig. 24. Measurement results of the noise detector output across varying DCO gain and noise.

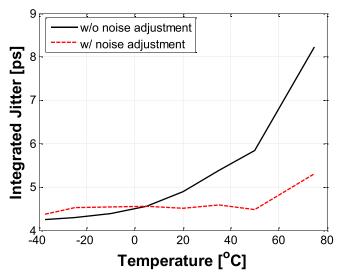

Fig. 25. Measurement results of the integrated jitter depending on the temperature.

The proposed noise detector assumes Gaussian distribution of output noise. However, DSM in the integral path generates quantization noise that does not follow Gaussian distribution,

Fig. 26. Phase noise measurement result when  $f_{\text{out}}$  is 2.4 GHz and the PLL is configured to the lowest noise mode.

Fig. 27. Die photogrpah of the proposed design.

and it can cause a discrepancy between the measurement and the theoretical calculation. This effect is more pronounced when the intrinsic DCO noise is small, i.e., when  $\sigma_{DCO}/\Phi_{lmt}$  is small, making DSM quantization noise non-negligible as shown in Fig. 24. The proposed PLL is tested with temperature sweep to verify the operation of noise self-adjustment. The DCO phase noise caused by device thermal noise is linear with temperature as shown in (32), whereas the PLL output jitter is proportional to the square of the DCO jitter because of the reduced bandwidth (42). Therefore, the PLL jitter has a quadratic relationship with temperature as it can be observed in Fig. 25. When the noise adjustment is enabled, the output noise remains relatively constant to the temperature change.

Fig. 26 shows the phase noise measurement results when the output frequency is 2.4 GHz and DCO is configured at a minimum noise state. The integrated phase noise is 2.522 ps while consuming 5 mW. A die photograph of the layout is

|                              | This work                                  | [35]   | [36]    | [37]   | [38]                  | [1]                | [39]     |          | [16]    |

|------------------------------|--------------------------------------------|--------|---------|--------|-----------------------|--------------------|----------|----------|---------|

| Output Frequency<br>(GHz)    | 0.8-3.2                                    | 3.2    | 2.4     | 1.6    | 0.2-3.8               | 0.2-3.2            | 0.8-1.8  |          | 2.4     |

| Oscillator Type              | Ring                                       | Ring   | Ring    | Ring   | Ring                  | Ring               | Ring     | MDLL     | MDLL    |

| Reference Frequency<br>(MHz) | 50                                         | 200    | 26      | 266    | 300                   | N/A                | 375      | 375      | 75      |

| RMS Integrated Jitter (ps)   | 3 @ 1GHz<br>2.7 @ 1.6GHz<br>2.52 @ 2.4GHz  | 3.85   | 2.418   | 2.418  | 2.13*                 | 3.1-14             | 3.2      | 0.4      | 0.7     |

| Integration Range<br>(MHz)   | 0.1-100                                    | N/A    | 0.01-40 | 0.01-2 | N/A*                  | 0.01-100           | 0.01-100 | 0.01-100 | 0.01-40 |

| Power Consumption (mW)       | 2.5 @ 1GHz<br>3.8 @ 1.6 GHz<br>5 @ 2.4 GHz | 2.915  | 6.4     | 2.7    | 1.98                  | 0.7-3.4            | 0.9      | 0.6      | 0.43    |

| Noise<br>Reconfiguration     | DCO<br>Noise & Pwr                         | N/A    | N/A     | N/A    | PLL Loop<br>Bandwidth | N/A                | N/A      | N/A      | N/A     |

| Figure of Merit (dB)         | -225.1 ~ -226.5                            | -224   | -221.6  | -226.7 | -230.5                | -224.8 ~<br>-218.6 | -228.59  | -248.7   | -246.7  |

| Area (mm²)                   | 0.049                                      | 0.0216 | 0.013   | 0.019  | 0.026                 | 0.017              | 0.2      | 0.2      | 0.024   |

| Technology                   | 28nm SOI                                   | 40nm   | 40nm    | 65nm   | 65nm                  | 22nm               | 130nm    | 130nm    | 28nm    |

TABLE I

PERFORMANCE SUMMARY OF THE PROPOSED DESIGN AND COMPARISON TO PRIOR ARTS OF INDUCTORLESS DESIGNS

Measured as time-interval error

displayed in Fig. 27. Table I compares the performance of the proposed PLL with previous works using ring oscillators. The proposed work provides a wide output frequency range of 0.8–3.2 GHz. Also this paper shows less than 3-ps integrated jitter while using a cost effective 50-MHz reference. Overall, the proposed PLL shows competitive performance compared with the previous works while providing power and noise reconfiguration and noise self-adjustment capability.

# VI. CONCLUSION

In this paper, a digital PLL using a nested FLL as a DCO is introduced. The proposed DCO provides accurate gain insensitive to the environmental changes as its period is locked to an *R*–*C* constant. Also, phase noise of the DCO can be controlled using a bias current so it can be adaptively tuned according to the noise specification. Further, a noise detection and self-adjustment scheme are proposed to maintain constant noise performance under the environmental changes. The proposed work showed wide noise reconfigurability from 2.5 to 15 ps while controlling its power consumption from 1.5 to 5 mW.

# APPENDIX A DETAILED PHASE NOISE DERIVATION

Equations (30)–(33) are calculated as follows:

$$L_{C_{sw}}(f) = A_{\text{noise}}^2 \frac{\overline{i_{1,\text{out}}^2}}{I_{\text{bias}}^2} \frac{f_{\text{out}}^2}{f^2}$$

$$= A_{\text{noise}}^2 \alpha^2 \frac{4kT}{I_{\text{bias}} V_{\text{sw}}} \frac{f_{\text{out}}^2}{f^2} = \frac{4kT}{I_{\text{bias}} V_{\text{sw}}} \frac{f_{\text{out}}^2}{f^2}$$

(A1)

$$L_{M_{1}}(f) = A_{\text{noise}}^{2} \frac{\overline{i_{2,\text{out}}^{2}}}{I_{\text{bias}}^{2}} \frac{f_{\text{out}}^{2}}{f^{2}}$$

$$= A_{\text{noise}}^{2} (1 - \alpha)^{2} \frac{4k \Gamma \gamma_{n} g_{m1}}{I_{\text{bias}}^{2}} \frac{f_{\text{out}}^{2}}{f^{2}} = \left(\frac{1 - \alpha}{\alpha}\right)^{2}$$

$$\times \frac{4k \Gamma \gamma_{n} g_{m1}}{I_{\text{bias}}^{2}} \frac{f_{\text{out}}^{2}}{f^{2}}$$

$$\times \frac{4k \Gamma \gamma_{n} g_{m1}}{I_{\text{bias}}^{2}} \frac{f_{\text{out}}^{2}}{f^{2}}$$

$$= A_{\text{noise}}^{2} \frac{\overline{i_{3,\text{out}}^{2}}}{I_{\text{bias}}^{2}} \frac{f_{\text{out}}^{2}}{f^{2}}$$

$$= A_{\text{noise}}^{2} \beta^{2} \frac{4k \Gamma}{I_{\text{bias}}^{2} R} \frac{f_{\text{out}}^{2}}{f^{2}} = \frac{\beta^{2}}{\alpha^{2}} \frac{4k \Gamma}{I_{\text{bias}} V_{R}} \frac{f_{\text{out}}^{2}}{f^{2}}$$

$$= A_{\text{noise}}^{2} \frac{\overline{i_{4,\text{out}}^{2}}}{I_{\text{bias}}^{2}} \frac{f_{\text{out}}^{2}}{f^{2}}$$

$$= A_{\text{noise}}^{2} (1 - \beta)^{2} \frac{4k \Gamma \gamma_{n} g_{m1}}{I_{\text{bias}}^{2}} \frac{f_{\text{out}}^{2}}{f^{2}} = \left(\frac{1 - \beta}{\alpha}\right)^{2}$$

$$\times \frac{4k \Gamma \gamma_{n} g_{m1}}{I_{\text{bias}}^{2}} \frac{f_{\text{out}}^{2}}{f^{2}}.$$

(A4)

Then, noise generated from the represented in terms of voltage ratios as follows:

$$L_{M_1}(f) = \frac{\text{mv}_T}{V_{\text{sw}}^2} \frac{4k \text{T} \gamma_n}{I_{\text{bias}}} \frac{f_{\text{out}}^2}{f^2}$$

(A5)

$$L_{M_2}(f) = A_{\text{noise}}^2 \frac{\text{mv}_T}{(V_R + \text{mv}_T)^2} \frac{4k\text{T}\gamma_p}{I_{\text{bias}}} \frac{f_{\text{out}}^2}{f^2}.$$

(A6)

The overall noise can be found by making summation of (A1), (A3), (A5), and (A6) which is shown in (32).

#### APPENDIX B

# PHASE NOISE CALCULATION WHEN TRANSISTORS ARE OPERATING AT A SATURATION REGION

In Section III, phase noise analysis of the proposed DCO is presented when the transistors,  $M_1$  and  $M_2$  in Fig. 1 are biased at a subthreshold region to maximize their transconductance. Sometimes, it is not possible to increase the gate size large enough to bias them at a subthreshold region due to area or gate leakage. In this appendix, phase noise of the proposed DCO with devices in a saturation region is discussed.

The current division ratio  $\alpha$  (24) can be rewritten by the following equation when  $M_1$  is biased at a saturation region:

$$\alpha = \frac{\frac{V_{\text{sw}}}{I_{\text{bias}}}}{\frac{V_{\text{sw}}}{I_{\text{bias}}} + \frac{V_{\text{gs,m1}} - V_{\text{thn}}}{2I_{\text{bias}}}} = \frac{2V_{\text{sw}}}{2V_{\text{sw}} + V_{\text{gs,m1}} - V_{\text{thn}}}$$

$$= \frac{2V_{\text{sw}}}{2V_{\text{sw}} + V_{\text{ov,m1}}}$$

(B1)

where  $V_{\rm gs}$  and  $V_{\rm ov}$  are the gate-to-source voltage and the overdrive voltage, respectively. Similarly, the current division ratio at the source of  $M_2$ ,  $\beta$ , is

$$\beta = \frac{2V_R}{2V_R + V_{\text{ov},m2}}.$$

(B2)

By replacing  $\alpha$  and  $\beta$  in (31) and (33) to (A1) and (A2), the phase noise contributions from  $M_1$  and  $M_2$  can be found as

$$L_{M_{1},Sat}(f) = \left(\frac{V_{\text{ov},m1}}{2V_{\text{sw}}}\right)^{2} \frac{8kT\gamma_{n}}{I_{\text{bias}}V_{\text{ov},m1}} \frac{f_{\text{out}}^{2}}{f^{2}}$$

$$= \frac{V_{\text{ov},m1}}{V_{\text{sw}}^{2}} \frac{2kT\gamma_{n}}{I_{\text{bias}}} \frac{f_{\text{out}}^{2}}{f^{2}}$$

$$L_{M_{2},Sat}(f) = A_{\text{noise}}^{2} \left(\frac{V_{\text{ov},m2}}{2V_{R} + V_{\text{ov},m2}}\right)^{2} \frac{8kT\gamma_{p}}{I_{\text{bias}}V_{\text{ov},m2}} \frac{f_{\text{out}}^{2}}{f^{2}}$$

$$= A_{\text{noise}}^{2} \frac{V_{\text{ov},m2}}{(2V_{R} + V_{\text{ov},m2})^{2}} \frac{8kT\gamma_{p}}{I_{\text{bias}}} \frac{f_{\text{out}}^{2}}{f^{2}}.$$

(B4)

Finally, the overall phase noise of the proposed FLL can be described as the following equation when  $M_1$  and  $M_2$  are in a saturation region:

$$L_{\text{Sat}}(f) = \frac{4kT}{I_{\text{bias}}} \left( \frac{1}{V_{\text{sw}}} \left( 1 + \frac{\gamma_n V_{\text{ov},m1}}{2V_{\text{sw}}} \right) + A_{\text{noise}}^2 \left( \frac{4V_R + 2\gamma_p V_{\text{ov},m2}}{(2V_R + V_{\text{ov},m2})^2} \right) \right) \frac{f_{\text{out}}^2}{f^2}.$$

(B5)

# REFERENCES

- [1] N. August, H.-J. Lee, M. Vandepas, and R. Parker, "A TDC-less ADPLL with 200-to-3200MHz range and 3mW power dissipation for mobile SoC clocking in 22nm CMOS," in *IEEE Int. Solid-State Circuits Conf.* (*ISSCC*) Dig. Tech. Papers, Feb. 2012, pp. 246–248.

- [2] J. Tierno et al., "A DPLL-based per core variable frequency clock generator for an eight-core POWER7 microprocessor," in Proc. Symp. VLSI Circuits, Jun. 2010, pp. 85–86.

- [3] A. Rylyakov et al., "Bang-bang digital PLLs at 11 and 20GHz with sub-200fs integrated jitter for high-speed serial communication applications," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2009, pp. 94–95 and 95a.

- [4] M. S.-W. Chen, D. Su, and S. Mehta, "A calibration-free 800 MHz fractional-N digital PLL with embedded TDC," *IEEE J. Solid-State Circuits*, vol. 45, no. 12, pp. 2819–2827, Dec. 2010.

- [5] S. Kim et al., "A 2 GHz synthesized fractional-N ADPLL with dual-referenced interpolating TDC," IEEE J. Solid-State Circuits, vol. 51, no. 2, pp. 391–400, Feb. 2016.

- [6] T.-K. Jang et al., "A 0.026mm<sup>2</sup> 5.3mW 32-to-2000MHz digital fractional-N phase locked-loop using a phase-interpolating phase-todigital converter," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2013, pp. 254–255.

- [7] M. Zanuso, S. Levantino, C. Samori, and A. L. Lacaita, "A wideband 3.6 GHz digital ΔΣ fractional-N PLL with phase interpolation divider and digital spur cancellation," *IEEE J. Solid-State Circuits*, vol. 46, no. 3, pp. 627–638, Mar. 2011.

- [8] R. B. Staszewski et al., "All-digital PLL and transmitter for mobile phones," *IEEE J. Solid-State Circuits*, vol. 40, no. 12, pp. 2469–2482, Dec. 2005

- [9] C. Weltin-Wu, E. Temporiti, D. Baldi, and F. Svelto, "A 3GHz fractional-N all-digital PLL with precise time-to-digital converter calibration and mismatch correction," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2008, pp. 344–345.

- [10] N. D. Dalt, "A design-oriented study of the nonlinear dynamics of digital bang-bang PLLs," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 52, no. 1, pp. 21–31, Jan. 2005.

- [11] N. D. Dalt, "Markov chains-based derivation of the phase detector gain in bang-bang PLLs," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 53, no. 11, pp. 1195–1199, Nov. 2006.

- [12] S. Tertinek, J. P. Gleeson, and O. Feely, "Binary phase detector gain in bang-bang phase-locked loops with DCO jitter," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 57, no. 12, pp. 941–945, Dec. 2010.

- [13] S. Jang, S. Kim, S.-H. Chu, G.-S. Jeong, Y. Kim, and D.-K. Jeong, "An all-digital bang-bang PLL using two-point modulation and back-ground gain calibration for spread spectrum clock generation," in *Proc. Symp. VLSI Circuits*, Jun. 2015, pp. C136–C137.

- [14] C.-M. Hsu, M. Z. Straayer, and M. H. Perrott, "A low-noise wide-BW 3.6-GHz digital ΔΣ fractional-N frequency synthesizer with a noise-shaping time-to-digital converter and quantization noise cancellation," *IEEE J. Solid-State Circuits*, vol. 43, no. 12, pp. 2776–2786, Dec. 2008.

- [15] R. Farjad-Rad et al., "A low-power multiplying DLL for low-jitter multigigahertz clock generation in highly integrated digital chips," *IEEE J. Solid-State Circuits*, vol. 37, no. 12, pp. 1804–1812, Dec. 2002.

- [16] H. Kim, Y. Kim, T. Kim, H. Park, and S. Cho, "19.3 A 2.4GHz 1.5mW digital MDLL using pulse-width comparator and double injection technique in 28nm CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2016, pp. 328–329.

- [17] S. H. Cho, "Self-noise cancelling technique for voltage-controlled oscillators," *Electron. Lett.*, vol. 44, no. 25, pp. 1436–1437, Dec. 2008.

- [18] C. Zhai, J. Fredenburg, J. Bell, and M. P. Flynn, "An N-path filter enhanced low phase noise ring VCO," in *Symp. VLSI Circuits Dig. Tech. Papers*, Jun. 2014, pp. 1–2.

- [19] R. Navid, T. H. Lee, and R. W. Dutton, "Minimum achievable phase noise of RC oscillators," *IEEE J. Solid-State Circuits*, vol. 40, no. 3, pp. 630–637, Mar. 2005.

- [20] A. A. Abidi, "Linearization of voltage-controlled oscillators using switched capacitor feedback," *IEEE J. Solid-State Circuits*, vol. SSC-22, no. 3, pp. 494–496, Jun. 1987.

- [21] K. Ueno, T. Asai, and Y. Amemiya, "A 30-MHz, 90-ppm/°C fully-integrated clock reference generator with frequency-locked loop," in *Proc. ESSCIRC*, Sep. 2009, pp. 392–395.

- [22] T. Jang, M. Choi, S. Jeong, S. Bang, D. Sylvester, and D. Blaauw, "5.8 A 4.7nW 13.8ppm/°C self-biased wakeup timer using a switchedresistor scheme," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2016, pp. 102–103.

- [23] M. Choi, T. Jang, S. Bang, Y. Shi, D. Blaauw, and D. Sylvester, "A 110 nW resistive frequency locked on-chip oscillator with 34.3 ppm/°C temperature stability for system-on-chip designs," *IEEE J. Solid-State Circuits*, vol. 51, no. 9, pp. 2106–2118, Sep. 2016.

- [24] M. Youssef, A. Zolfaghari, H. Darabi, and A. Abidi, "A low-power wideband polar transmitter for 3G applications," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2011, pp. 378–380.

- [25] N. Sasidhar, R. Inti, and P. K. Hanumolu, "Low-noise self-referenced CMOS oscillator," *Electron. Lett.*, vol. 45, no. 18, pp. 920–921, Aug. 2009.

- [26] T. Jang, S. Jeong, D. Jeon, K. D. Choo, D. Sylvester, and D. Blaauw, "8.4 A 2.5ps 0.8-to-3.2GHz bang-bang phase- and frequency-detectorbased all-digital PLL with noise self-adjustment," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2017, pp. 148–149.

- [27] K. Y. J. Shen et al., "19.4 A 0.17-to-3.5mW 0.15-to-5GHz SoC PLL with 15 dB built-in supply noise rejection and self-bandwidth control in 14 nm CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2016, pp. 330–331.

- [28] A. Elshazly, R. Inti, W. Yin, B. Young, and P. K. Hanumolu, "A 0.4-to-3GHz digital PLL with supply-noise cancellation using deterministic background calibration," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2011, pp. 92–94.

- [29] Z. Z. Chen et al., "14.9 Sub-sampling all-digital fractional-N frequency synthesizer with -111 dBc/Hz in-band phase noise and an FOM of -242 dB," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech.* Papers, Feb. 2015, pp. 1–3.

- [30] W. Kim, J. Park, H. Park, and D.-K. Jeong, "Layout synthesis and loop parameter optimization of a low-jitter all-digital pixel clock generator," *IEEE J. Solid-State Circuits*, vol. 49, no. 3, pp. 657–672, Mar. 2014.

- [31] T. Anand, M. Talegaonkar, A. Elshazly, B. Young, and P. K. Hanumolu, "A 2.5GHz 2.2mW/25 μmW on/off-state power 2psrms-long-term-jitter digital clock multiplier with 3-reference-cycles power-on time," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2013, pp. 256–257.

- [32] M. Zanuso, D. Tasca, S. Levantino, A. Donadel, C. Samori, and A. L. Lacaita, "Noise analysis and minimization in bang-bang digital PLLs," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 56, no. 11, pp. 835–839, Nov. 2009.

- [33] J. Lee, K. S. Kundert, and B. Razavi, "Analysis and modeling of bangbang clock and data recovery circuits," *IEEE J. Solid-State Circuits*, vol. 39, no. 9, pp. 1571–1580, Sep. 2004.

- [34] M. Seok, G. Kim, D. Blaauw, and D. Sylvester, "A portable 2-transistor picowatt temperature-compensated voltage reference operating at 0.5 V," *IEEE J. Solid-State Circuits*, vol. 47, no. 10, pp. 2534–2545, Oct. 2012.

- [35] C.-W. Yeh, C.-E. Hsieh, and S.-I. Liu, "19.5 A 3.2GHz digital phase-locked loop with background supply-noise cancellation," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2016, pp. 332–333.

- [36] Y.-C. Huang, C.-F. Liang, H.-S. Huang, and P.-Y. Wang, "A 2.4GHz ADPLL with digital-regulated supply-noise-insensitive and temperatureself-compensated ring DCO," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2014, pp. 270–271.

- [37] B. Kim, S. Kundu, and C. H. Kim, "A 0.4–1.6GHz spur-free bang-bang digital PLL in 65 nm with a D-flip-flop based frequency subtractor circuit," in *Proc. Symp. VLSI Circuits*, Jun. 2015, pp. C140–C141.

- [38] J. Crossley, E. Naviasky, and E. Alon, "An energy-efficient ringoscillator digital PLL," in *Proc. IEEE Custom Integr. Circuits Conf.*, Sep. 2010, pp. 1–4.

- [39] A. Elshazly, R. Inti, B. Young, and P. K. Hanumolu, "A 1.5GHz 890 μmW digital MDLL with 400fsrms integrated jitter, -55.6 dBc reference spur and 20fs/mV supply-noise sensitivity using 1b TDC," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2012, pp. 242–244.

**Seokhyeon Jeong** (S'12) received the B.S. degree in electrical engineering from the Korea Institute of Science and Technology, Seoul, South Korea, in 2011, and the Ph.D. degree in electrical engineering from the University of Michigan, Ann Arbor, MI, USA, in 2017.

He is currently with CubeWorks, Ann Arbor, where he is researching and developing interface circuits for ultra-low-power sensor nodes. His current research interests include ultra-low-power temperature sensor, A/D converter, and the design

of millimeter-scale computing systems.

**Dongsuk Jeon** received the B.S. degree in electrical engineering from Seoul National University, Seoul, South Korea, in 2009, and the Ph.D. degree in electrical engineering from the University of Michigan, Ann Arbor, MI, USA, in 2014.

From 2014 to 2015, he was a Post-Doctoral Associate with the Massachusetts Institute of Technology, Cambridge, MA, USA. He is currently an Assistant Professor with the Graduate School of Convergence Science and Technology, Seoul National University. His current research interests include

energy-efficient signal processing, low-power circuit, and SoC for mobile applications.

Taekwang Jang (S'06) received the B.S. and M.S. degrees in electrical engineering from KAIST, Daejeon, South Korea, in 2006 and 2008, respectively. Since 2013, he has been pursuing the Ph.D. degree with the University of Michigan, Ann Arbor, MI, USA.

In 2008, he joined Samsung Electronics Company Ltd., Giheung, South Korea, where he focused on mixed-signal circuit design including analog and all-digital phase-locked loops for communication systems and mobile processors fabricated in 20–45-nm

CMOS process. His current research interests include clock generation, data converters, and ultra-low-power system design.

Dr. Jang was a co-recipient of the 2009 IEEE Circuits and Systems Society Guillemin-Cauer Best Paper Award.

**Kyojin David Choo** (S'13) received the B.S. and M.S. degrees in electrical engineering and computer science from Seoul National University, Seoul, South Korea, in 2007 and 2009, respectively. He is currently pursuing the Ph.D. degree in electrical and computer engineering from the University of Michigan, Ann Arbor, MI, USA.

From 2009 to 2013, he was with Image Sensor Development Team of Samsung Electronics, Giheung, South Korea, where he developed analog/mixed-signal readout circuits. He has focused

on high-speed serial links, PLL/DLLs, and precision analog circuits. His current research interests include low-power sensor design, millimeter-scale system integration, and low-noise timing generation circuits.

**Dennis Sylvester** (S'95–M'00–SM'04–F'11) received the Ph.D. degree in electrical engineering from the University of California, Berkeley, CA, USA.

He is currently a Professor of electrical engineering and computer science, University of Michigan, Ann Arbor, MI, USA, where he is also the Director with the Michigan Integrated Circuits Laboratory, a group of ten faculties and 70+graduate students. He held research staff positions with the Advanced Technology Group, Synopsys,

Mountain View, CA, USA; and the Hewlett-Packard Laboratories, Palo Alto, CA, USA; and Visiting Professorships with the National University of Singapore, Singapore, and Nanyang Technological University, Singapore. He has authored or co-authored over 450 articles along with one book and several book chapters. He has 34 U.S. patents. He also serves as a Consultant and Technical Advisory Board Member for electronic design automation and semiconductor firms in his research areas. His current research interests include the design of millimeter-scale computing systems and energy-efficient near-threshold computing

Dr. Sylvester was a recipient of an NSF CAREER Award, the Beatrice Winner Award at ISSCC, an IBM Faculty Award, an SRC Inventor Recognition Award, and ten Best Paper Awards and nominations. He was named one of the Top Contributing Authors at ISSCC and was awarded the University of Michigan Henry Russel Award for distinguished scholarship. He served on the Executive Committee of the ACM/IEEE Design Automation Conference. He serves on the Technical Program Committee of the IEEE International Solid-State Circuits Conference. He is the co-founder of Ambig Micro. He has served as an Associate Editor for the IEEE TRANSACTIONS ON COMPUTER-AIDED DESIGN OF INTEGRATED CIRCUITS AND SYSTEMS and the IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION SYSTEMS, and the Guest Editor for the IEEE JOURNAL OF SOLID-STATE CIRCUITS and the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS II. His dissertation was recognized with the David J. Sakrison Memorial Prize as the most outstanding research with the Department of Electrical Engineering and Computer Sciences University of California, Berkeley.

**David Blaauw** (M'94–SM'07–F'12) received the B.S. degree in physics and computer science from Duke University, Durham, NC, USA, in 1986, and the Ph.D. degree in computer science from the University of Illinois at Urbana–Champaign, Champaign, IL, USA, in 1991.

Until 2001, he was with Motorola, Inc., Austin, TX, USA, where he was the Manager with the High Performance Design Technology Group. Since 2001, he has been on the Faculty of the University of Michigan, Ann Arbor, MI, USA, where he is

currently a Professor. He has extensive research in ultra-low-power computing using subthreshold computing and analog circuits for millimeter sensor systems and for high-end servers, his research group and collaborators introduced so-called near-threshold computing, which has become a common concept in semiconductor design. This work led to a complete sensor node design with record low power consumption, which was selected by the MIT Technology Review as one of the year's most significant innovations. He has pursued research in cognitive computing using analog, in-memory neural networks. He has authored or co-authored over 500 papers and holds 60 patents. His research has a threefold focus.

Dr. Blaauw was a recipient of the Motorola Innovation Award, the Numerous Best Paper Awards and nominations, 2016 SIA-SRC Faculty Award for lifetime research contributions to the U.S. semiconductor industry. He has investigated adaptive computing to reduce margins and improve energy efficiency using a new approach he pioneered, called Razor, for which he received the Richard Newton GSRC Industrial Impact Award and the IEEE Micro annual Top-Picks Award. He was the General Chair of the IEEE International Symposium on Low Power, the Technical Program Chair for the ACM/IEEE Design Automation Conference, and serves on the IEEE International Solid-State Circuits Conference's Technical Program Committee.