# A Fully Integrated, Automatically Generated DC–DC Converter Maintaining >75% Efficiency From 398 K Down to 23 K Across Wide Load Ranges in 12-nm FinFET

Anhang Li<sup>®</sup>, *Graduate Student Member, IEEE*, Jeongsup Lee<sup>®</sup>, Prashansa Mukim, Brian D. Hoskins, Pragya Shrestha<sup>®</sup>, David Wentzloff<sup>®</sup>, *Senior Member, IEEE*, David Blaauw<sup>®</sup>, *Fellow, IEEE*, Dennis Sylvester<sup>®</sup>, and Mehdi Saligane

Abstract—This letter presents a fully integrated recursive successive-approximation switched capacitor (RSC) DC-DC converter implemented using an automatic cell-based layout generation in 12-nm FinFET technology. A novel design methodology is demonstrated based on the theoretical analyses of the optimal energy operation of the switched-capacitor (SC) DC-DC converter and directly finds the optimal design parameters from the given input specifications. The converter maintains >75% efficiency across a vast range of output currents and temperatures. Our design targets voltage scaling for applications, such as cryo-computing, cryo-sensing, and parts of quantum computing, to achieve high-system power efficiency.

*Index Terms*—Cryogenic, DC-DC, switched-capacitor (SC), wide temperature.

#### I. INTRODUCTION

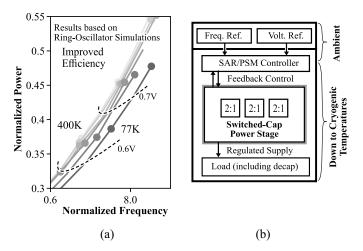

There has been a renewed interest in utilizing cryogenic CMOS electronics to realize performance enhancements in various applications, including high-performance computing [1], [2], qubit systems [3], sensors, superconductivity, and other low-temperature applications in sectors, such as those found in aerospace [4]. Fig. 1 summarizes practical applications that require operation from normal conditions down to cryogenic temperatures and would benefit from cryogenic CMOS design techniques. To satisfy the low-thermal limit of dilution refrigerators, improved power efficiency is required for circuit components located within the cooling chamber as well as circumvent electrical noise generated due to self-heating. This requirement demands efficient power distribution and conversion. Ring-oscillator (RO) simulations, shown in Fig. 2(a), display temperature effects on digital circuit performance: as we get closer to cryogenic conditions, mobility  $(\mu)$  increases, resulting in both a higher speed and higher-power consumption, yet having generally a better-energy efficiency. Fig. 2(b) illustrates how the recursive switched capacitor DC-DC (RSC) DC-DC converter proposed in this letter can be integrated into a cryogenic IC system close to the extreme temperature region to help facilitate voltage scaling. We experimentally demonstrate our 3-stage converter

Manuscript received 3 October 2023; revised 8 December 2023; accepted 17 December 2023. Date of publication 1 January 2024; date of current version 19 January 2024. This article was approved by Associate Editor Xin Zhang. (Corresponding author: Mehdi Saligane.)

Anhang Li, Jeongsup Lee, David Wentzloff, David Blaauw, Dennis Sylvester, and Mehdi Saligane are with the EECS Department, University of Michigan, Ann Arbor, MI 48109 USA (e-mail: mehdi@umich.edu).

Prashansa Mukim is with the Physical Measurement Laboratory, National Institute of Standards and Technology, Gaithersburg, MD 20899 USA, and also with the Department of Chemistry and Biochemistry, University of Maryland, College Park, MD 20742 USA.

Brian D. Hoskins and Pragya Shrestha are with the Physical Measurement Laboratory, National Institute of Standards and Technology, Gaithersburg, MD 20899 USA.

Digital Object Identifier 10.1109/LSSC.2023.3349129

Fig. 1. Typical applications of cryo-electronics.

Fig. 2. Power scaling and cryogenic system power hierarchy. (a) Simulated power saving using voltage scaling from 400K to 77K. (b) Cryogenic electronic system power hierarchy design.

targeting operation temperature from 398 K down to 23 K, with efficiency >75%.

# II. RSC DC-DC IMPLEMENTATION AND METHODOLOGY

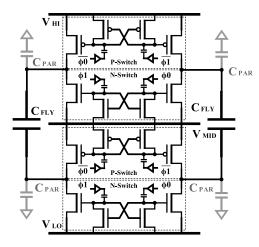

A RSC consists of a chain of 2:1 switched capacitor conversion cells [5]. In addition to the power efficiency advantage demonstrated in [5], the RSC architecture is chosen because it contains parallel multiples of exactly two manually designed unit cell layouts, making it easy for us to analyze and implement automated layout generation.

# A. Circuit Implementation

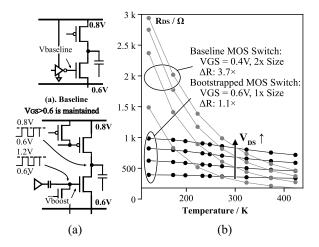

Fig. 3 shows the schematic of a 2:1 cell. We propose to drive the switches with bootstrap drivers to provide a higher-gate voltage  $(V_{\text{boost}})$  and reduce source-drain resistance  $(R_{DS,ON})$ . A higher- $V_{GS}$  over larger device sizing is preferred. This is advantageous when the temperature is extremely low because The transistor threshold voltage  $(V_{TH})$  increases drastically at cryogenic temperatures [6], leading to a massive increase in  $R_{DS,ON}$  for regular switches as shown in Fig. 4(a). The effectiveness of this design choice is illustrated

2573-9603 © 2024 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

Fig. 3. Circuit implementation of the 2:1 conversion cell.

Fig. 4. Bootstrapped RSC switch. (a) Baseline. (b) Bootstrapped. (c) Regular versus bootstrapped switch RDS comparison.

in our simulation results Fig. 4(c). Since e did not have access to cryogenic SPICE models in the 12-nm finFET technology node, we relied on prior publications to estimate the behavior of all elements in our circuit, such as MOSFETs [7] and passive components [8]. This allowed us to estimate the circuit's performance. Our circuit validation was post-fabrication. Additionally, since all the transistors in our design are isolated using deep-Nwell, the parasitic diode has no risk of turning on or causing significant deviation from the expected results.

## B. RSC's Design Parameter Optimization

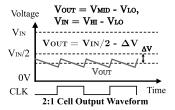

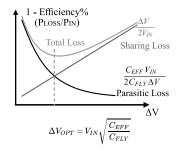

1) Capacitive Loss Analysis: The derivation starts with analyzing the switching waveform, shown in Fig. 5: when the load current is zero, the 2:1 converter output equals  $V_{\rm IN}/2$ ; when a current draw occurs, the  $V_{OUT}$  will decrease by  $\Delta V$ . In an ideal switched capacitor system with zero resistive loss, the power loss comes from two sources: 1) the sharing loss  $(L_S)$  when injecting charges from the flying capacitor into the output capacitor and 2) the loss in the parasitic capacitance  $(L_P)$ . Analysis of the two main capacitive loss mechanisms has shown an optimal  $\Delta V$  that corresponds to the maximum efficiency [9]. This is shown graphically in Fig. 6.

$^{1}$ This simulation uses an extrapolated model. The vendor guarantees accuracy from 218K to 423K. The  $R_{DS,ON}$  discussion is mainly based on [6] instead of this plot.

Fig. 5. Switching waveform.

Fig. 6. Switched capacitor loss analysis.

Fig. 7. MOSFET switch loss analysis.

Equation set (1). is the equation extended for N-stage RSC converters based on the assumption that  $\Delta V$  is averaged evenly across all stages.

$$P_{\text{IN}}(N) = \left(\sum_{i=1}^{N} 2\alpha_i C_i \left(\frac{\Delta V}{N}\right)^2 f_{\text{CLK}}\right) V_{\text{IN}}$$

(1a)

$$L_S(N) \approx \sum_{i=1}^{N} C_i \left(\frac{\Delta V}{N}\right)^2 f_{\text{CLK}} = C_{\text{FLY}} \left(\frac{\Delta V}{N}\right)^2 f_{\text{CLK}}$$

(1b)

$$L_P(N) \approx C_{EFF} V_{\text{IN}}^2 f_{\text{CLK}}$$

(1c)

$$\Delta V_{OPT} = N \cdot V_{\rm IN} \sqrt{\frac{C_{EFF}}{C_{\rm FLY}}}.$$

(1d)

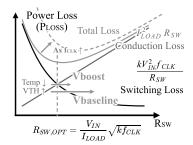

2) Optimization of Switch Sizing: The goal of transistor sizing is to balance the loss due to switch resistance (conduction loss) and the loss due to the capacitive parasitic (switching loss). This is shown graphically in Fig. 7. The dashed curve shows how the curve will move as frequency increases. An ideal feedback controller provides a maximum efficiency point tracking (MEPT) mechanism that modulates the clock frequency to track the lowest point on this curve for the least loss. From Fig. 7, the optimal switch impedance is given by (2) where *k* is the coefficient relating to the parasitic capacitance and resistance of a unit-size MOSFET switch

$$R_{\rm SW,OPT} = \frac{V_{\rm IN}}{I_{\rm LOAD}} \sqrt{k f_{\rm CLK}}.$$

(2)

3) Process/Temperature Variation Considerations: As shown in (1b), the optimal  $\Delta V$  is expressed as a ratio. Where  $C_{\rm EFF}$  is primarily contributed by routing capacitance while  $C_{\rm FLY}$  variations

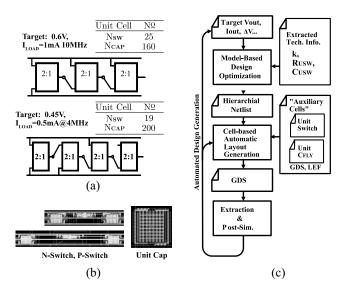

Fig. 8. Diagram of the automated flow [10]. (a) Some example configurations. (b) "Auxiliary Cell" building blocks. (c) Automated design flow.

Fig. 9. RSC fixed-ratio 7:8 converter for tapeout.

TABLE I CONSTANTS USED DURING DERIVATION

| Symbol                      | Meaning                                                      |  |  |  |

|-----------------------------|--------------------------------------------------------------|--|--|--|

| $\alpha_i$                  | Up/Down Configuration of Stage i                             |  |  |  |

| $\Delta V$                  | Voltage Delta due to Current Draw                            |  |  |  |

| $C_{EFF}$                   | Effective Parasitic Capacitance                              |  |  |  |

| $C_{FLY}$                   | Flying Capacitance                                           |  |  |  |

| $k = R_{USW} \cdot C_{USW}$ | Approximated relationship of switch resistance & capacitance |  |  |  |

| $C_{UFLY}$                  | Unit Capacitor Cell Capacitance                              |  |  |  |

| $R_{USW}$                   | Unit Switch Cell On-State Resistance                         |  |  |  |

| $C_{USW}$                   | Unit Switch Cell Parasitic Capacitance                       |  |  |  |

are attenuated and result in a nearly constant  $\Delta V$  across process variation. The relationship between  $R_{SW,OPT}$  and  $f_{CLK}$  is not constant due to the change in mobility under different corners. To achieve optimal efficiency when the switch resistance is the limiting factor (technology dependent), calibration has to be done on a prechip basis.

# C. Cell-Based Layout Generator

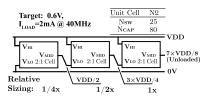

Now that  $\Delta V$  is fixed as a meta-parameter, the optimized capacitor and switch sizing can be expressed in an integer amount of unit cells. The extended synthesis formula set (3) is converted into a Pythonbased design generation flow Fig. 8(c). Fig. 8(a) shows some example synthesized optimal designs

$$I_{\text{LOAD}} = 2C_{\text{FLY}(\text{laststage})} \frac{\Delta V}{N} f_{\text{CLK}}$$

(3a)

$$I_{\text{LOAD}} = 2C_{\text{FLY(laststage)}} \frac{\Delta V}{N} f_{\text{CLK}}$$

(3a)

$$N_{\text{CAP(laststage)}} = \frac{N \cdot I_{\text{LOAD}}}{2\Delta V f_{\text{CLK}} C_{\text{FLY(unit)}}}$$

(3b)

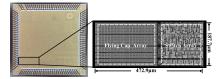

Fig. 10. Die photograph and GDS top view.

Fig. 11. Test setup. (a) Test setup diragram. (b) Test setup photograph.

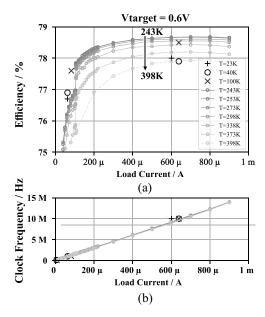

Power efficiency and output voltage swept across load current, Fig. 12. frequency, and temperature.

$$N_{\text{SW(laststage)}} = \frac{I_{\text{LOAD}}R_{\text{SW(unit)}}}{\sqrt{k}V_{\text{IN}}\sqrt{f_{\text{CLK}}}}.$$

(3c)

A 3-stage converter optimized for 0.6 V, 2-mA output at 40 MHz, shown in Fig. 9, is taped out in a 12-nm FinFET process. The fabricated chip is shown in Fig. 10.

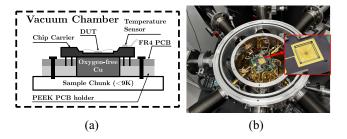

## III. CRYOGENIC MEASUREMENTS

The chip setup was placed in a cryo-chamber and cooled by a closed-cycle refrigerator (CCR). Limited by the physical size of the assembly, the lowest temperature achievable is 22.5K. Before the test, >1-h soaking is given to ensure temperature stability. Fig. 11(a) shows the detailed measurement setup.

The converter's power efficiency and output voltage are measured across a wide range of frequencies, temperature (398K to 23K), and output loads (2  $\mu$ A to 4 mA). A passive variable resistor is used as

Fig. 13. Closed-loop efficiency and clock frequency plots across a wide temperature range. (a) Maximum efficiency versus load current. (b) Frequency versus load current at maximum efficiency tracking.

TABLE II COMPARISON WITH RELATED WORKS

| Metric                               | This<br>Work                                     | [13]                             | [14]                                                               | [11]                                                    | [5]                                           | [12]                      |

|--------------------------------------|--------------------------------------------------|----------------------------------|--------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------|---------------------------|

| Architec-<br>ture                    | RSC -<br>Fixed                                   | Tunable<br>or Fixed              | Fixed 2:1<br>LC Reson.                                             | RSC -<br>Tunable<br>or Fixed                            | RSC -<br>Tunable<br>or Fixed                  | LDO                       |

| Wide<br>Temp.<br>Range               | Yes<br>(23K-<br>400K)                            | -                                | -                                                                  | -                                                       | -                                             | No<br>(4K<br>Only)        |

| Tech-<br>nology                      | 12nm                                             | 22nm                             | 45nm SOI<br>Integ. Ind.                                            | 350nm<br>HVCMOS                                         | 250nm                                         | 22nm<br>SOI               |

| Input<br>Voltage                     | 0.8V                                             | 1.23V                            | 1V                                                                 | 2~13V                                                   | 2.5V                                          | 1.8V                      |

| Output<br>Voltage                    | 0.6V                                             | 0.45~<br>1V                      | 0.35~<br>0.41V                                                     | 5V                                                      | 0.1∼<br>2.2V                                  | 1.5V                      |

| Reported<br>Effi-<br>ciency<br>Range | 75%<br>@ 400K,<br>0.1mA;<br>80%<br>@ 23K,<br>1mA | <70%<br>@ 0.55V<br>84%<br>@ 1.1V | 75.5%@<br>0.44A/mm <sup>2</sup><br>70.2%@<br>0.92A/mm <sup>2</sup> | 81.5%<br>@10.7V in<br>1.3mA;<br><30%<br>@2V in<br>0.2mA | 85%<br>Peak;<br><70%@<br>0.1A/mm <sup>2</sup> | -                         |

| Load<br>Range                        | ${<1 \mu A} \atop {\sim 2 \mathrm{mA}}$          | 88mA                             | 25~295mA                                                           | 0.2mA &<br>1.3mA                                        | 2mA                                           | 64mA<br>@ 3.7K            |

| Current<br>Density                   | 0.02<br>A/mm <sup>2</sup>                        | 0.38<br>A/mm <sup>2</sup>        | 0.92<br>A/mm <sup>2</sup>                                          | 0.0013<br>A/mm <sup>2</sup>                             | 0.0028<br>A/mm <sup>2</sup>                   | 1.43<br>A/mm <sup>2</sup> |

| Drop-<br>Out                         | 0.2V                                             | 0.68V                            | 0.65V                                                              | -                                                       | 0.3V                                          | 0.3V                      |

a load, with a 1- $\mu$ F capacitor in parallel. The measurement results plotted in Fig. 12 show the peak efficiency points at each input clock frequency. The output voltage  $V_{\rm OUT}$  remains close to the design target of 0.6V. Fig. 13 shows the measured efficiency when an external feedback loop is applied to regulate the output using pulse density modulation (PDM) [5]; the design's efficiency varies by less than 3% across the tested temperature range, with a high-control linearity of  $R^2 = 0.99$ .

#### IV. CONCLUSION

This letter presents an automated framework for a cryogenic switched-capacitor (SC) DC-DC converter design generation, based

on an innovative optimal sizing methodology, demonstrated by silicon measurement results under cryogenic temperatures. Measure results of our proposed design are highlighted in comparison Table II. The converter delivers comparable power efficiency to prior art [11] across wide load ranges at very low-drop-out voltage due to the low- $R_{DS,ON}$  design. Compared to a previously reported high-performance cryogenic LDO design [12], our converter is able to cover a much wider [23K, 398K] temperature range and was measured at NIST.

Code Availability: The source code is available in [10].

#### ACKNOWLEDGMENT

The authors would like to thank the defense advanced research projects agency (DARPA) and Google for their support.

## REFERENCES

- [1] H. L. Chiang et al., "Cold CMOS as a power-performance-reliability booster for advanced FinFETs," in *Proc. IEEE Symp. VLSI Technol.*, 2020, pp. 1–2.

- [2] D. Prasad et al., "Cryo-computing for infrastructure applications: A technology-to-microarchitecture co-optimization study," in *Proc. Int. Electr. Devices Meet. (IEDM)*, 2022, pp. 23.5.1–23.5.4.

- [3] M. Mehrpoo et al., "Benefits and challenges of designing cryogenic CMOS RF circuits for quantum computers," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, 2019, pp. 1–5.

- [4] S.-H. Hong, G.-B. Choi, R.-H. Baek, H.-S. Kang, S.-W. Jung, and Y.-H. Jeong, "Low-temperature performance of Nanoscale MOSFET for deep-space RF applications," *IEEE Electr. Device Lett.*, vol. 29, no. 7, pp. 775–777, Jul. 2008.

- [5] L. G. Salem and P. P. Mercier, "A recursive switched-capacitor DC–DC converter achieving 2<sup>N</sup> 1 ratios with high efficiency over a wide output voltage range," *IEEE J. Solid-State Circuits*, vol. 49, no. 12, pp. 2773–2787, Dec. 2014.

- [6] M. Shin et al., "Low temperature characterization of mobility in 14-nm FD-SOI CMOS devices under interface coupling conditions," *Solid-State Electron.*, vol. 108, pp. 30–35, Jun. 2015. [Online]. Available: https://www.sciencedirect.com/science/article/pii/S0038110114003062

- [7] H.-C. Han, F. Jazaeri, A. D'Amico, A. Baschirotto, E. Charbon, and C. Enz, "Cryogenic characterization of 16-nm FinFET technology for quantum computing," in *Proc. IEEE 47th Eur. Solid State Circuits Conf.* (ESSCIRC), 2021, pp. 71–74.

- [8] B. Patra, M. Mehrpoo, A. Ruffino, F. Sebastiano, E. Charbon, and M. Babaie, "Characterization and analysis of on-chip microwave passive components at cryogenic temperatures," *IEEE J. Electr. Devices Soc.*, vol. 8, pp. 448–456, 2020.

- [9] W. Jung et al., "An ultra-low power fully integrated energy harvester based on self-oscillating switched-capacitor voltage doubler," *IEEE J. Solid-State Circuits*, vol. 49, no. 12, pp. 2800–2811, Dec. 2014.

- [10] idea fasoc. "FASoC." 2023. [Online]. Available: https://github.com/idea-fasoc/fasoc

- [11] D. Lutz, P. Renz, and B. Wicht, "12.4 a 10mW fully integrated 2-to-13V-input buck-boost SC converter with 81% peak efficiency," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, 2016, pp. 224–225.

- [12] D. Andrade-Miceli et al., "Cryogenic low-drop-out regulators fully integrated with quantum dot array in 22-nm FD-SOI CMOS," in *Proc. IEEE MTT-S Int. Microw. Symp. (IMS)*, 2021, pp. 635–637.

- [13] R. Jain et al., "A 0.45–1 V fully-integrated distributed switched capacitor DC–DC converter with high density MIM capacitor in 22-nm Tri-gate CMOS," *IEEE J. Solid-State Circuits*, vol. 49, no. 4, pp. 917–927, Apr. 2014.

- [14] M. Abdelfattah, M. Swilam, B. Dupaix, S. Smith, A. Fayed, and W. Khalil, "An on-chip resonant-gate-drive switched-capacitor converter for near-threshold computing achieving 70% efficiency at 0.92A/mm<sup>2</sup> current density and 0.4V output," in *Proc. IEEE Int. Solid-State Circuits Conf. (ISSCC)*, 2018, pp. 438–440.