# A Light-Tolerant Wireless Neural Recording IC for Motor Prediction With Near-Infrared-Based Power and Data Telemetry

Jongyup Lim<sup>10</sup>, Member, IEEE, Jungho Lee<sup>10</sup>, Graduate Student Member, IEEE,

Eunseong Moon<sup>10</sup>, Member, IEEE, Michael Barrow<sup>10</sup>, Graduate Student Member, IEEE,

Gabriele Atzeni<sup>(D)</sup>, *Graduate Student Member, IEEE*, Joseph G. Letner, Joseph T. Costello<sup>(D)</sup>,

Samuel R. Nason<sup>®</sup>, Paras R. Patel<sup>®</sup>, Yi Sun<sup>®</sup>, Parag G. Patil, Hun-Seok Kim<sup>®</sup>, *Member, IEEE*,

Cynthia A. Chestek, Member, IEEE, Jamie Phillips<sup>®</sup>, Senior Member, IEEE, David Blaauw<sup>®</sup>, Fellow, IEEE,

Dennis Sylvester<sup>(D)</sup>, Fellow, IEEE, and Taekwang Jang<sup>(D)</sup>, Senior Member, IEEE

Abstract-Miniaturized and wireless near-infrared (NIR)based neural recorders with optical powering and data telemetry have been introduced as a promising approach for safe long-term monitoring with the smallest physical dimension among stateof-the-art standalone recorders. However, the main challenge for the NIR-based neural recording integrated circuits (ICs) is to maintain robust operation in the presence of light-induced parasitic short-circuit current from junction diodes. This is especially true when the signal currents are kept small to reduce power consumption. In this work, we present a light-tolerant and low-power neural recording IC for motor prediction that can fully function in up to 300  $\mu$ W/mm<sup>2</sup> of light exposure. It achieves the best-in-class power consumption of 0.57  $\mu$ W at 38 °C with a 4.1 noise efficiency factor (NEF) pseudo-resistor-less amplifier, an on-chip neural feature extractor, and individual mote-level gain control. Applying the 20-channel pre-recorded neural signals of a monkey, the IC predicts finger position and velocity with

Manuscript received August 21, 2021; revised November 19, 2021; accepted December 23, 2021. Date of publication January 25, 2022; date of current version March 28, 2022. This article was approved by Associate Editor Borivoje Nikolić. This work was supported by the National Institutes of Health under Grant 5R21EY029452-02. (*Corresponding author: Jongyup Lim.*)

This work involved human subjects or animals in its research. Approval of all ethical and experimental procedures and protocols was granted by the University of Michigan's Institutional Animal Care and Use Committee.

Jongyup Lim, Jungho Lee, Eunseong Moon, Michael Barrow, Joseph T. Costello, Yi Sun, Hun-Seok Kim, David Blaauw, and Dennis Sylvester are with the Department of Electrical and Computer Engineering, University of Michigan, Ann Arbor, MI 48109 USA (e-mail: jongyup@umich.edu).

Gabriele Atzeni and Taekwang Jang are with the Department of Information Technology and Electrical Engineering, ETH Zürich, 8092 Zürich, Switzerland.

Joseph G. Letner, Samuel R. Nason, and Paras R. Patel are with the Department of Biomedical Engineering, University of Michigan, Ann Arbor, MI 48109 USA.

Parag G. Patil is with the Department of Neurological Surgery, Neurology, Anesthesiology, and Biomedical Engineering, University of Michigan, Ann Arbor, MI 48109 USA.

Cynthia A. Chestek is with the Department of Biomedical Engineering and Electrical Engineering and Computer Science, University of Michigan, Ann Arbor, MI 48109 USA.

Jamie Phillips is with the Department of Electrical and Computer Engineering, University of Delaware, Newark, DE 19716 USA.

Color versions of one or more figures in this article are available at https://doi.org/10.1109/JSSC.2022.3141688.

Digital Object Identifier 10.1109/JSSC.2022.3141688

a correlation coefficient up to 0.870 and 0.569, respectively, with individual mote-level gain control enabled. In addition, wireless measurement is demonstrated through optical power and data telemetry using a custom photovoltaic (PV)/light-emitting diode (LED) GaAs chip wire bonded to the proposed IC.

*Index Terms*—Brain-computer interface (BCI), brainmachine interface (BMI), neural implant, wireless neural recording, wireless sensor node.

# I. INTRODUCTION

**N** RAIN–MACHINE interface (BMI) or brain–computer Dinterface (BCI) has been developed with the initial goal of restoring function for people who are paralyzed, amputated, or suffer from neuromuscular disorders. Recent research on neural electrode probes [1]-[7] and neural recording application-specific integrated circuits (ASICs) [7]-[11] has enabled efficient high-channel recording and decoding along with new findings of various neural features and the development of decoding algorithms. However, the array of wires required for power and data communication and the bulky form factor of the neural recording ASICs has limited the use of conventional high-channel recording systems [7]–[11]. Although flexible electrode wires [5]–[7] alleviate some of the challenges, the associated tethering forces increase the risk of scar tissue and thus prevent safe and long-term monitoring of neural activity.

To address this challenge, different free-floating neural recorders have been proposed with miniaturized size, a characteristic critical to achieving dense recording sites and minimum brain damage. These miniaturized standalone freefloating motes include only single channel per mote rather than multi-channels with denser array of electrodes. While the latter approach can achieve very small intra-mote channel pitch, the chip size needs to be increased accordingly and, hence, results in similar average pitch between channels. Therefore, in terms of acquiring multiple independent sources of information, regular spacing of the single-channel freefloating motes is preferable to supersampling small spatial

0018-9200 © 2022 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

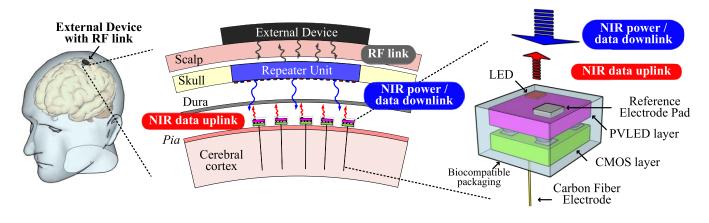

Fig. 1. Conceptual illustration of two-step wireless neural recording system and NIR-based free-floating motes.

regions with wide gaps between groups of channels of multichannel free-floating motes. A near-field RF-based neural grain [12], [13] is one such system. The neural grain records electrocorticography (ECoG) signals with near-field RF-based power transfer and bidirectional communication. In [13], *in vivo* measurement with multiple implanted neural grains is demonstrated; however, the remaining challenge is that 0.5 W of transceiver (Tx) power is required to operate  $0.5 \text{ mm} \times 0.5 \text{ mm}$  RF-based neural grains, which exceeds the safety regulations by  $10 \times [12]$ . Another approach utilizes ultrasound for wireless power transfer and data link. Ghanbari et al. [14] introduced an ultrasound-based neural dust that adopts amplitude modulation (AM) backscattering for data telemetry, achieving low nonlinearity below 1.2%. However, it requires a 0.75 mm  $\times$  0.75 mm  $\times$  0.75 mm bulky piezoceramic, which results in an overall dust size of 0.8 mm<sup>3</sup>. Alternatively, in [15] and [16], a near-infrared (NIR) light is exploited for power and data telemetry using a custom photovoltaic (PV) cell and light-emitting diodes (LEDs). The NIR-based neural recorder reported in [15] achieves the smallest size, 0.25 mm  $\times$  0.06 mm, reported to date among stateof-the-art standalone free-floating neural recorders. However, lacks data downlink capability and the surface electrode of the mote only allows surface potential monitoring or injection of the whole mote into brain tissue, which can cause bleeding or tissue damage.

In [16], a 0.74- $\mu$ W 0.19 mm × 0.17 mm NIR-based wireless neural recorder with random chipID [17] and on-chip neural feature extraction is proposed. It is designed based on the two-step wireless neural recording concept described in Fig. 1. In the envisioned system, numerous free-floating motes are placed in the sub-dural space to record neural activities, while only carbon fiber electrodes with less than 10  $\mu$ m diameter [18] penetrate several millimeters into the brain tissue. As the carbon fiber electrodes have been shown to incur minimal chronic scar formation [18], the proposed system can improve the long-term sustainability significantly. A repeater unit in the epidural space (Fig. 1, center) powers and programs free-floating motes by emitting 850-nm NIR lights. A custom dual-junction PV layer on top of the CMOS circuit layer of the free-floating motes harvests the energy.

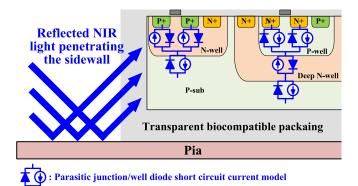

Fig. 2. Cross section of the CMOS circuit layer with light-induced parasitic short-circuit currents.

At the same time, the optical receiver (ORx) translates light modulation into digital data. A custom micro-LED transmits data by firing LED pulses so that the repeater unit receives the pulses emitted from multiple motes using an array of singlephoton avalanche diodes (SPADs) to decode them using the random chipIDs of the motes.

This work uses the same system architecture as that proposed in [16] and builds on it by proposing a new CMOS circuit layer that addresses the challenge of light tolerance. Although most of the perpendicular light used to power the motes is absorbed by the GaAs-based PV layer [19] that sits on top of the CMOS circuit layer, the reflected and scattered 850-nm NIR light still can penetrate through the sidewalls of the free-floating motes (Fig. 2), impacting overall circuit performance. Furthermore, the sub- $\mu$ W circuit with limited supply current is particularly susceptible to lightinduced parasitic short-circuit currents. In conventional chip packaging, the light can be blocked using an opaque encapsulant, whereas NIR-based free-floating motes need the PV layer and LED exposed to the light for wireless powering and data communication. A partly transparent encapsulation that exposes the PV layer and LED only and blocks light for the CMOS circuit layer is problematic for sub-mm-level packaging. Therefore, a light-tolerant circuit design is essential for the robust operation of the envisioned neural recording system.

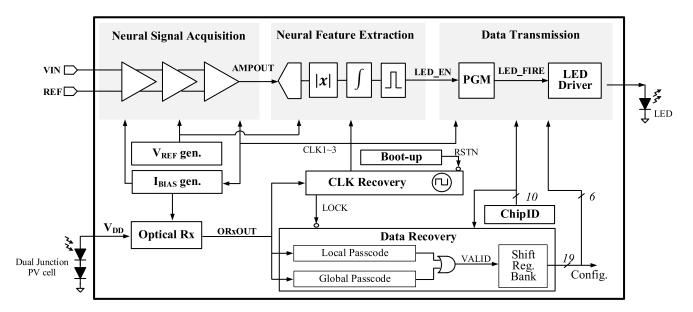

Fig. 3. Top circuit diagram of the proposed light-tolerant neural recorder.

To address this challenge, we proposed a light-tolerant neural recording integrated circuit (IC) for NIR-based freefloating motes that wireless operate under 150  $\mu$ W/mm<sup>2</sup> of target optical power density [20]. It achieves light-robust operation up to 300  $\mu$ W/mm<sup>2</sup> of NIR light power density, whereas the baseline implementation fails at 8  $\mu$ W/mm<sup>2</sup> [16]. In addition, the proposed design includes on-chip feature extraction and individual mote-level gain control capability with an overall power consumption of 0.57  $\mu$ W, which is the lowest among the state-of-the-art free-floating motes [13]–[16].

This article is organized as follows. Section II provides the system overview and discusses the light robustness. Section III describes the light-tolerant circuit implementation. Section IV presents the measurement results, and finally, Section V concludes this article.

## II. SYSTEM OVERVIEW AND LIGHT ROBUSTNESS

# A. System Overview

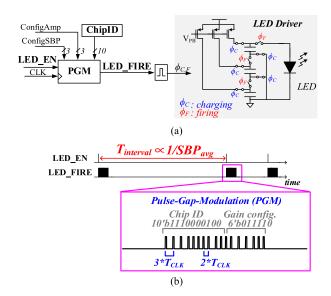

The circuit diagram of the proposed neural recorder is shown in Fig. 3. The main signal chain is composed of three stages: neural signal acquisition, neural feature extraction, and data transmission. The neural signal acquisition block consists of a three-stage bandpass low-noise amplifier (LNA) to acquire single neuron-level spikes that are probed by the carbon fiber electrode [18]. It also passes the signal with the frequency band of interest through precise bandpass filtering. In this work, we focus on the 300–1000-Hz band to extract a neural feature called spiking band power (SBP) [21]-[23]. SBP is defined as the absolute average of the signal amplitude in the 300-1000-Hz band, and this neural feature is known for achieving high motor prediction accuracy relative to a standard 7.5-kHz high-bandwidth neural recording despite its low-bandwidth output [21]-[23]. By computing the SBP on-chip, the data uplink communication bandwidth is reduced

to a maximum of hundreds of Hz, thereby saving uplink power and uplink channel capacity. Furthermore, the SBP is computed with energy- and area-efficient circuits (described in Section III). The acquired SBP data are encoded in symbolinterval modulation (SIM) of uplink LED packets to avoid data conversion overhead. A single uplink LED packet consists of 16-b pulse-gap-modulated (PGM) data, including the random chipID [17].

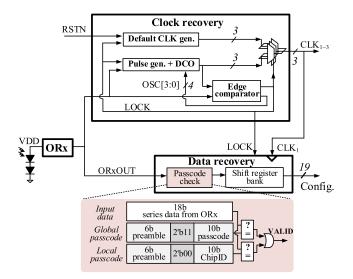

Due to the dual-junction PV cell of the custom GaAs chip [19], 1.5–1.6 V of supply voltage is directly supplied to the chip, eliminating on-chip dc-dc conversion overhead. The vertically stacked dual-junction PV cell in [19] has junctions with the identical GaAs-based materials and bandgap energies. It is designed to achieve equal optical absorption at each of the junctions doubling the voltage output while reducing the number of lateral series connections and shunt leakage paths. The PV cell generates  $I_{SC} = 1.1 \ \mu A$  and  $V_{OC} = 1.6 \ V$  at 150  $\mu$ W/mm<sup>2</sup> of target 850-nm NIR light power density, where 190  $\mu$ W/mm<sup>2</sup> is the maximum NIR optical power density for human dura as evaluated in [19]. In addition, ac modulation of the NIR light power is translated into digital modulation by ORx to execute clock and data recovery (CDR). The clock recovery circuit locks the on-chip clock to the modulation frequency of the light. This recovered clock is used to set an accurate corner frequency of the bandpass transfer function of the amplifier chain using the bias currents generated from the switched capacitor. Note that the clock recovery is done globally at the initial start-up phase of the multiple probes. It makes an array of probes to be locked to the same target frequency; therefore, the corner and the bias current of each probe can be set accurately based on their recovered frequency, minimizing the impact of process and voltage variation across probes. The data recovery block receives the serial data from the pulsewidth modulation (PWM) of the NIR light and programs the chip configurations, including the gain setting of the amplifier and SBP extraction unit.

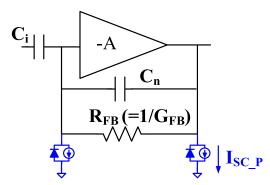

Fig. 4. Capacitive amplifier with the feedback resistor  $R_{\text{FB}}$  and parasitic light-induced short-circuit current  $I_{\text{SC}_{P}}$ .

#### B. Light-Induced Current and Light Robustness

Unlike conventional chip design with opaque encapsulation, the proposed system must maintain its performance under the condition where NIR photons invade from the sidewall and bounce around the CMOS layer. Basically, when photons hit any p-n junction within the CMOS circuit layer (Fig. 2), the light-induced carriers by the p-n junctions cause a movement of holes to the p-side and electrons to the n-side, which is known as a PV effect [24]. In other words, every p-n junction may act as a small solar cell that generates short-circuit current ( $I_{SC}$ ) that is proportional to the light power intensity and junction area [25]:

$$I_{\rm SC} = {\rm SR} \cdot P_{\rm NIR}(\lambda) = \left(\frac{q\lambda}{\rm hc}\right) {\rm EQE} \cdot I_{\rm NIR}(\lambda) \cdot A_{\rm junc} \qquad (1)$$

where SR is the spectral responsivity, EQE is the external quantum efficiency,  $I_{\text{NIR}}$  is the NIR light intensity, and  $A_{\text{junc}}$  is the junction surface area. Any conducting path in the proposed system, especially for analog blocks with high impedance paths, can be affected by the parasitic light-induced short-circuit current ( $I_{\text{SC}_P}$ ). If there is any  $I_{\text{SC}_P}$  flowing in or out of the conducting path between nodes X and Y, we define the light robustness coefficient (LRC) of the conducting path as follows:

$$\alpha_{\rm LR} = \left(\frac{I_{XY}}{\sum I_{\rm SC\_P}}\right) \cdot \left(\frac{1}{V_{XY}}\right) = \frac{G_{XY}}{\sum I_{\rm SC\_P}}[V^{-1}] \qquad (2)$$

where  $I_{XY}$ ,  $V_{XY}$ , and  $G_{XY}$  are, respectively, the original conducting current, the voltage difference, and the conductance of the path between nodes X and Y when there is no light at all. If a conducting path has significantly high conductance over the sum of  $I_{SC P}$  in the path, then the path is barely impacted by the light and therefore achieves high light robustness (high  $\alpha_{LR}$ ). On the other hand, if a path has low  $\alpha_{LR}$ , it is susceptible to light. One example is a capacitive amplifier with the feedback resistor  $R_{\rm FB}$  (Fig. 4). In many applications including neural recording or biomedical sensing, a high  $R_{\rm FB}$  (or low  $G_{\rm FB}$ ) is required to achieve a low-to-highpass corner frequency  $(f_{\rm HP})$ . In conventional designs with opaque encapsulation, total  $I_{SC_P}$  is zero, so no consideration of  $\alpha_{LR}$  is needed. However, in the proposed NIR-based neural recorder, it is critical to implement a high  $R_{\rm FB}$  in the neural amplifier chain while simultaneously achieving a high  $\alpha_{LR}$ ,

a feat that is very challenging. The proposed neural recorder is designed with the consideration of  $\alpha_{LR}$  in every building block to achieve overall light robustness of the system.

## **III. CIRCUIT IMPLEMENTATION**

#### A. R<sub>PSD</sub>-Less Neural Amplifier

A pseudo resistor,  $R_{PSD}$ , is frequently used for dc biasing or feedback of the amplifier [Table I (left)] of a miniaturized neural recording IC [15], [16] since it can easily achieve over a few T $\Omega$  of high impedance with only a few transistors, which results in an overall compact layout area. However,  $R_{PSD}$  not only has poor process sensitivity but also cannot avoid an extremely low  $\alpha_{LR}$  [Table I (left)]. With  $R_{PSD}$ , the dc-bias level drifts at <1  $\mu$ W/mm<sup>2</sup> of light intensity in simulation, whereas we need  $R_{\rm FB}$  that can sustain at least 150  $\mu$ W/mm<sup>2</sup>of light intensity. Light tolerance of  $R_{PSD}$ -based structure can be improved using photo-induced current compensation technique [26]; however, the high process sensitivity of  $R_{PSD}$  still remains as the main challenge using  $R_{PSD}$  as  $R_{FB}$ . Another  $R_{\rm FB}$  type adopting a series-to-parallel switched capacitor was introduced in [27] and improves process sensitivity. Due to its higher  $G_{\rm FB}$ , the series-to-parallel switched capacitor achieves significantly higher  $\alpha_{LR}$  than  $R_{PSD}$ ; however, its high number of switches results in a large total junction area and high  $I_{SC P}$ , and thus,  $\alpha_{LR}$  is still too low (Table I, middle). In this work, we designed a  $3 \times$  voltage attenuator and increased the input and the feedback capacitor by the same factor to maintain  $f_{\rm HP}$ similar to the series-to-parallel switched-capacitor approach, as shown in (3) and (5)

$$f_{\text{HP},s-\text{to}-p} c_s = \frac{1}{2\pi} \cdot \left(\frac{C_s f_{\text{CLK}}}{10}\right) \cdot \frac{1}{C_n}$$

$$= \left(\frac{1}{20\pi}\right) \cdot \left(\frac{C_s}{C_n}\right) \cdot f_{\text{CLK}}$$

(3)

$$G_{\text{FB},s-\text{to}-p\ Cs} = \left(\frac{1}{10}\right) \cdot C_s f_{\text{CLK}} \tag{4}$$

$$f_{\text{HP,proposed}} = \frac{1}{2\pi} \cdot \left(\frac{C_s f_{\text{CLK}}}{3}\right) \cdot \frac{1}{3C_n}$$

$$= \left(\frac{1}{18\pi}\right) \cdot \left(\frac{C_s}{C_n}\right) \cdot f_{\text{CLK}}$$

(5)

$$G_{\rm FB, proposed} = C_s f_{\rm CLK}.$$

(6)

While maintaining a similar level of  $f_{\rm HP}$ , the proposed approach achieves around  $10 \times G_{\rm FB}$  compared with seriesto-parallel switched-capacitor-based approach, as shown in (4) and (6), while having a lower  $I_{\rm SC_P}$  resulting in a 5 × 10<sup>4</sup>× and 46× improvement in  $\alpha_{\rm LR}$  compared with  $R_{\rm PSD}$ -based and series-to-parallel switched-capacitor-based approaches, respectively (Table I).

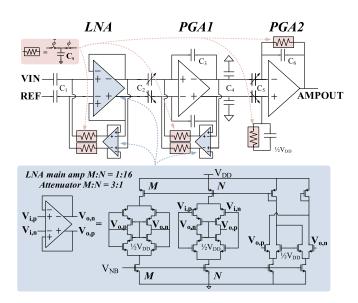

In this work, we propose a three-stage neural amplifier composed of an LNA followed by two programmable-gain amplifiers (PGAs) [Fig. 5 (top)]. The gains of the LNA and feedback attenuators of LNA and PGA1 are set by the transconductance ( $g_m$ ) ratio as shown in the bottom of Fig. 5 to avoid large area occupation of capacitors in the conventional capacitive amplifiers [28]. Operational transimpedance amplifier (OTA) in [28] with an inverter-based input stage is

| $R_{FB}$ Type                              | $R_{PSD}$                                | Series-to-parallel Cs [27]                                        | Attenuator + $C_S$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|--------------------------------------------|------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Structure                                  |                                          |                                                                   | $\begin{array}{c} \overbrace{\left(\frac{1}{18\pi}\right)\left(\frac{C_s}{C_n}\right)}^{\overbrace{\left(\frac{1}{18\pi}\right)}} 3C_i \\ 3C_i \\ -A \\ 3C_n \\ 3C_n \\ -A \\ -A \\ 3C_n \\ -A \\ -$ |  |

| $f_{HP}$                                   | $(\frac{1}{2\pi})(\frac{1}{R_{PSD}C_n})$ | $\left(\frac{1}{20\pi}\right)\left(\frac{C_s}{C_n}\right)f_{clk}$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| $G_{FB}$ [pS]                              | 0.16                                     | 9.1                                                               | 117.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| $I_{SC P}$ [pA]                            | 1375                                     | 63                                                                | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| $\alpha_{LR} (= G_{FB}/I_{SC P}) [V^{-1}]$ | 0.00012                                  | 0.14                                                              | 6.52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

TABLE I

Simulated Light Robustness of Three Different Feedback Resistors

\*  $I_{SC P}$  proportional to junction area is modeled in simulation

\*\* Simulation parameters:  $R_{PSD} = 6.3T\Omega$ ,  $C_S = 11$  fF,  $f_{CLK} = 8$  kHz, each junction-to-well area  $= 0.25 \mu$ m<sup>2</sup>, p-well-to-deep-n-well area of  $R_{PSD} = 15 \mu$ m<sup>2</sup>

Fig. 5. Proposed light robust neural amplifier chain.

implemented with cascode N/PMOS transistors included in both input and output stage of the OTA [Fig. 5 (bottom)]. In the subthreshold region,  $g_m$  is proportional to bias current, and therefore, the OTA gain can be accurately controlled by bias current ratio of input and output stage. Power consumption of each attenuator is 19.4 nW (5.4% of the total amplifier) providing sufficient bandwidth for constant attenuation across the main signal bandwidth, whereas noise contribution of the attenuators is negligible compared to the thermal noise of effective  $R_{\rm FB}$  located at the same noise transfer path of the attenuators. Area overhead of the proposed structure mainly comes from the MIM and MOM combined input capacitor  $C_1$ (6.9 pF), while  $C_2$  and  $C_3$  are only 0.4 and 2.5 pF, respectively (Fig. 5). The amplifier achieves 23 M $\Omega$  of input impedance at 1 kHz, which is an order of magnitude larger than the 1-kHz impedance of the carbon fiber electrode, which varies from sub-M $\Omega$  for short-term implant to few-M $\Omega$  for long-term implant [18].

The differential-to-single-ended PGA2 implements a simple switched-capacitor resistor for  $R_{\rm FB}$  to set  $f_{\rm HP}$  of the overall transfer function of the amplifier chain. In PGA2, the proposed  $3 \times$  feedback attenuator  $+ 3 \times$  input and feedback capacitor scheme are not required since the simple switched-capacitor resistor already satisfies high  $\alpha_{\rm LR}$  and the target  $f_{\rm HP}$ . PGA2 also operates as a gm-*C* filter that sets a low-pass corner frequency ( $f_{\rm LP}$ ) of the amplifier chain. As the amplifier operates in the sub-threshold region, the transconductance is defined as follows:

$$g_m = \frac{I_{\rm DS}}{nV_T} \tag{7}$$

where  $I_{\text{DS}}$ , *n*, and  $V_T$  are the drain-to-source current, subthreshold slope, and thermal voltage, respectively.  $I_{\text{DS}}$  is set by  $I_{\text{REF}}$  generated by the switched-capacitor-based  $G_m$ biasing circuit; therefore, it is proportional to the switching capacitance,  $C_{\text{SW}}$ , and frequency

$$I_{\rm DS} = m \cdot I_{\rm REF} = k \cdot C_{\rm SW} \cdot f_{\rm CLK}.$$

(8)

From (3) and (4), the bandwidth of the gm-C filter is precisely defined by the capacitance ratio and clock frequency

$$f_{\rm LP} = \frac{g_m}{C_L} = \left(\frac{k}{nV_T}\right) \cdot \left(\frac{C_{\rm SW}}{C_L}\right) \cdot f_{\rm CLK}.$$

(9)

Therefore, both  $f_{\rm HP}$  and  $f_{\rm LP}$  are set by the capacitance ratio and  $f_{\rm CLK}$  recovered from the CDR. Amplifier dc offset is canceled from stage to stage by ac coupled capacitors, while the inner stage input offset is mitigated by the feedback loop gain.

#### B. Neural Feature Extraction Unit

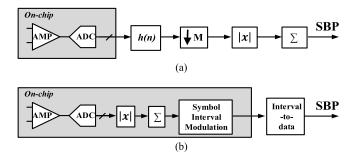

Given the extremely small power budget, we focus on the low-bandwidth neural feature called SBP for the motor function decoding to minimize the power consumption. In a conventional approach, SBP, which is defined as the absolute average of signal amplitude in the 300–1000-Hz band [21]–[23], is extracted using high-power ASICs to record a raw high-bandwidth neural signal and then filter it in the digital domain and perform absolute integration (Fig. 6). Instead,

Fig. 6. (a) Conventional approach of extracting SBP. (b) Proposed approach of extracting SBP.

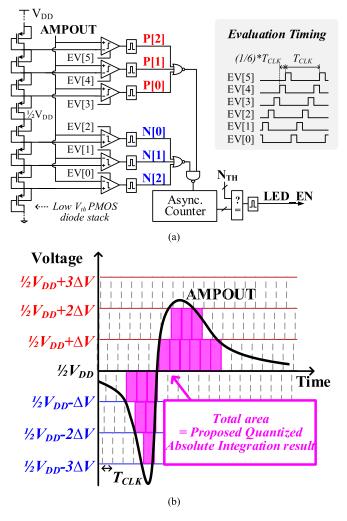

we introduced an energy-efficient and compact on-chip SBP extraction in the analog domain using the charge integration described in [16]. However, the analog domain SBP extractor in [16] relies on only tens of pA of on current to charge an integration capacitor, which is susceptible to  $I_{SC P}$ . In this work, we propose an area- and energy-efficient, light-tolerant digital SBP extraction unit using a 2.8-bit flash-ADC and pulse-counter-based integrator, as shown in Fig. 7(a). The proposed unit consists of a  $V_{\text{REF}}$  generator implemented with a diode stack (12 nA in simulation) and dynamic comparators operating with staggered clock signals with six different phases, followed by pulse generators. Due to the staggered clock signals with six different phases, all the evaluation edges  $(EV_{[5-0]})$  are non-overlapped. Therefore, the time-domain integration of the absolute amplitude could be done by simply combining six output pulses  $[P_{[0-2]} \text{ and } N_{[0-2]} \text{ in Fig. 7(a)}]$  by logic gates and counting them by a single shared asynchronous counter. As a result, the total quantized area of the AMPOUT signal in Fig. 7(b) is encoded in the time interval as the LED\_EN, which triggers the firing of an LED packet for data uplink. The threshold count  $N_{\text{TH}}$  in Fig. 7(a) can be updated to control the gain of the SBP extraction unit. All the components, including the  $V_{\text{REF}}$  generator, the dynamic comparators, and the digital circuits implemented with standard cells, meet the high  $\alpha_{LR}$  standard for light-robust operation. The dynamic comparators and digital standard cells have high drivability during the transition phase and strong retention in steady state significantly enhancing the light tolerance.  $V_{\text{REF}}$  generator is designed with sufficient supply current of 12 nA at the typical corner and 2.7 nA at the worst corner (simulation) to handle sub-nA level of total  $I_{SC P}$  with enough margin. The process variation and mismatch impact of the output voltage of  $V_{\text{REF}}$ generator on overall decoding performance and SBP extraction is minimized by two main factors. First, the decoding accuracy and SBP are highly correlated with the input spiking rate rather than the linearity of the signal amplitude. In addition, a single step of the quantized voltage,  $\Delta V$  in Fig. 7(b), is 130 mV, whereas its standard deviation across both process variation and mismatch is 6.2 mV (Monte Carlo (MC) simulation with 1000 samples) minimizing linearity degradation.

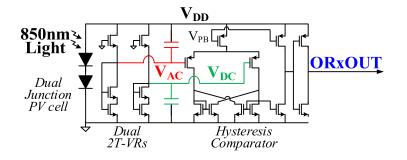

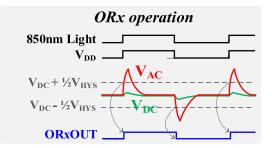

# C. Optical Receiver

An ORx is a key component for data downlink converting ac modulation of the NIR light intensity to the digital sequence

Fig. 7. (a) Proposed SBP extraction unit and (b) quantization of absolute amplitude and width from the SBP extraction unit.

that is needed for CDR. The main challenge of ORx is to receive low-frequency data modulated through the supply without having any low impedance path that is susceptible to light (poor  $\alpha_{LR}$ ). In this work, we propose a novel ORx utilizing a high-pass filter whose cutoff frequency is much higher than the modulation data rate by combining it with the hysteresis comparator. The ORx is composed of dual 2T-VRs [29]: one ac-coupled to  $V_{DD}$  and another to ground and a hysteresis comparator (Fig. 8). The 2T-VRs are sized for 1.4 nA of current in simulation to ensure high  $\alpha_{LR}$ , and the *RC*-time constant is set much shorter than the light modulation period but, still longer than the time constant of the hysteresis comparator. Therefore, the proposed ORx fetches the input modulation and maintains the output value until the next toggle.

# D. Pulse-Gap Modulator and LED Driver

The data transmission block, including PGM and an LED driver, receives the output of the SBP extraction unit and emits light using LED to the repeater unit. PGM encodes the 10-b random chipID [17] and 6-b AFE gain configuration

Fig. 8. Proposed dual 2T-VRs and hysteresis comparator-based ORx.

Fig. 9. (a) Proposed PGM and LED driver. (b) SIM and PGM.

(3 b for the amplifier and 3 b for the SBP extraction unit), 17 pulses total where the 16 pulse gaps of either  $2T_{CLK}$  or  $3T_{CLK}$  stand for data 0 or 1, respectively (Fig. 9). The 6-b AFE gain configuration in the uplink LED packet lets the external users know the current gain status and acts as an indicator of successful data recovery, which will be covered in Section III-E.

The custom LED [19] requires mA-level driving current to maximize external quantum efficiency (1% EQE at 0.1 mA and 2% EQE at 1 mA) and to maximize the detection rate of the repeater. However, the supply current of the chip is limited by the short-circuit current that the PV cell can generate  $(I_{\rm SC} = 1.1 \ \mu \text{A} \text{ at } 150 \ \mu \text{W/mm}^2 \text{ of NIR light [19]})$ . Therefore, we slowly charge three capacitors in parallel during the LED off time and up-convert the voltage using the series connection of three capacitors to provide instinct high driving voltage and current on LED ( $V_{\text{LED,PK}} = 2.15$  V and  $I_{\text{LED,PK}} = 3.73$  mA in simulation). The proposed PGM provides 2T<sub>CLK</sub> of long capacitor charging time of the LED driver, and this helps the LED driver to reduce the charging current level. LED\_EN from the SBP extraction unit toggles the 17 PGM LED light pulses, and the extracted SBP is encoded in the time interval between two adjacent LED\_EN signals or two LED packets

Fig. 10. Proposed CDR block.

[Fig. 9(b)]. This modulation scheme is referred to as PGMbased symbol-interval modulation (PGM-SIM).

# E. Clock and Data Recovery

In Fig. 10, a block diagram of the proposed CDR is introduced. In the power-ON reset phase, a default clock generator sends out default clock to the overall system, and the system enters the clock recovery phase. With the external NIR light modulated at a constant frequency of 8 kHz, the clock recovery block calibrates the digitally controlled oscillator (DCO) with a 4-b thermometer-coded control scheme to match the received modulation period with the DCO period (Fig. 10). After the DCO frequency is calibrated, the LOCK signal rises and switches the system clock from the default to the recovered clock using glitch-free multiplexers.

After the clock recovery phase, the system functions normally with the data recovery triggered whenever the passcode is received. The repeater unit programs the system by modulating the NIR light intensity with a PWM scheme, and it sends a total of 37-bit data composed of 18 bit for passcode and 19 bit for the system configuration (Fig. 10). There are two types of passcodes implemented: global and local. A global passcode is an 18-bit, fully hardwired code that is identical for every recording chip. Therefore, if the repeater sends out

Fig. 11. Die photograph.

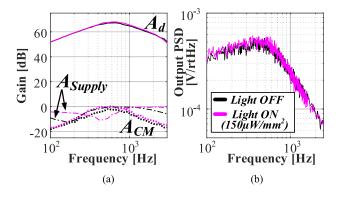

Fig. 12. (a) Measured amplifier ac performance and (b) output noise power spectral density.

a particular configuration with the global passcode, all the freefloating motes under the receiver update their configurations to the identical setup with single programming. On the other hand, a local passcode is composed of an 8-bit preamble plus 10-bit random chipID [17]. This allows individual remote gain control (RGC). Depending on the obtained neural signal magnitude at each mote, the repeater layer can program an individual chip without affecting other motes. This RGC capability enables flexible channel gain adaption, for instance, off-chip-level automatic gain control (AGC) by monitoring the average LED firing rate of every channel.

# **IV. MEASUREMENT RESULTS**

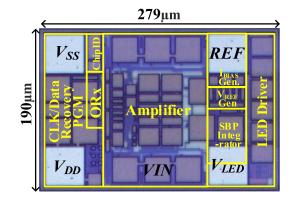

The proposed light-tolerant neural recording IC was fabricated in 180-nm CMOS (Fig. 11). The chip can fully function under 300  $\mu$ W/mm<sup>2</sup>of NIR optical power density, which exceeds the target optical power density for the real application (150  $\mu$ W/mm<sup>2</sup>). AFE performance was measured with a bare die exposed to NIR light, and a wireless measurement was performed by using a commercial NIR light source for power transfer and downlink. A commercial SPAD was used to receive uplink signals sent by the LED. In this setup, the proposed IC was wire-bonded with a custom PV/LED GaAs chip side-by-side without any other tethering wires. In addition, *in vivo* measurements were performed by connecting a carbon fiber inserted into the brain of an anesthetized Long Evans rat. Furthermore, a 20-channel prerecorded motor

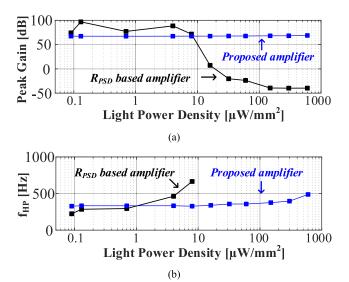

Fig. 13. (a) Measured peak gain and (b) high-pass corner sweeping NIR light intensity.

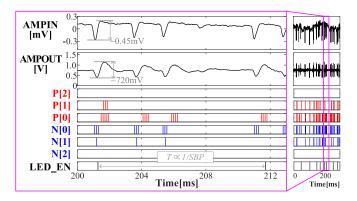

Fig. 14. Measured transient waveform of the SBP extraction unit under  $300-\mu$ W/mm<sup>2</sup> NIR light.

TABLE II Measured Amplifier AC Performance

| Light ON (150µW/mm <sup>2</sup> ) |  |  |

|-----------------------------------|--|--|

| 68.0                              |  |  |

| 2.2                               |  |  |

| 69.2                              |  |  |

| [380, 1060]                       |  |  |

| 13.5                              |  |  |

| 6.2                               |  |  |

| -                                 |  |  |

\* Measured in 38°C

cortex signal acquired by Utah microelectrode arrays was provided to the chip after the proper attenuation to emulate the *in vivo* measurement. Then, the finger movement of a monkey was predicted using the resulting SBP produced by the proposed IC.

# A. AFE Performance Under Bare Die Exposure to NIR Light

For AFE performance validation, the bare die was exposed to a commercial 850-nm light source (IRS4, CMVision) and the measurement was performed in a temperature chamber

|                                                     |                         | This work                | ISSCC 2020 [16]         | TBioCAS 2018 [15]    | NER 2019 [13]        | JSSC 2019 [14]       |

|-----------------------------------------------------|-------------------------|--------------------------|-------------------------|----------------------|----------------------|----------------------|

| Technology [nm]                                     |                         | 180                      | 180                     | 180                  | 65                   | 65                   |

| Wireless Method                                     |                         | Optical                  | Optical                 | Optical              | RF                   | Ultrasonic           |

| Area [mm <sup>2</sup> ]                             |                         | 0.053                    | 0.032                   | 0.014                | 0.250                | 0.250                |

| $(W[mm] \times L[mm])$                              |                         | $(0.19 \times 0.28)$     | $(0.19 \times 0.17)$    | $(0.25 \times 0.06)$ | $(0.50 \times 0.50)$ | $(0.50 \times 0.50)$ |

| Data<br>Link                                        | Uplink                  | PGM-SIM                  | Manchester-SIM          | PPM                  | RF                   | AM                   |

|                                                     | Downlink                | PWM                      | PWM                     | No                   | ASK-PWM              | No                   |

|                                                     | Mote-Level Gain Control | Yes                      | No                      | No                   | No                   | No                   |

| On-chip Feature Extraction                          |                         | SBP (digital)            | SBP (analog)            | No                   | No                   | No                   |

| Chip ID                                             |                         | Yes                      | Yes                     | No                   | Yes                  | Yes                  |

| Clock Recovery                                      |                         | Yes                      | Yes                     | No                   | No                   | No                   |

| Use of Pseudo Resistor                              |                         | No                       | Yes                     | Yes                  | No                   | No                   |

| Light Tolerant Design<br>(max. light power density) |                         | Yes<br>(300µW/mm²)       | No                      | No                   | N/A**                | N/A**                |

| Supply [V]                                          |                         | 1.55                     | 1.5                     | 0.9                  | 0.6                  | 1                    |

| Power                                               | Total [µW]              | 0.57 <sup>†</sup>        | 0.74 <sup>†</sup>       | 1                    | 40                   | 28.8                 |

|                                                     | Amplifier [µW]          | 0.36 <sup>†</sup>        | 0.51 <sup>†</sup>       | 0.5                  | 3.2                  | 4                    |

| Target neural signal                                |                         | AP                       | AP                      | LFP, AP              | ECoG                 | LFP, AP              |

| Gain [dB]                                           |                         | 67.2 <sup>†</sup>        | 69.0 <sup>†</sup>       | 30.0                 | N/A                  | 24.0                 |

| Bandwidth [Hz]                                      |                         | [350, 1080] <sup>†</sup> | [180, 950] <sup>†</sup> | 10000                | 500                  | 5000                 |

| CMRR [dB]                                           |                         | 69.7                     | N/A*                    | N/A*                 | N/A*                 | N/A*                 |

| PSRR [dB]                                           |                         | 67.5                     | N/A*                    | N/A*                 | N/A*                 | N/A*                 |

| IRN [µV <sub>RMS</sub> ]                            |                         | 6.2 <sup>†</sup>         | 4.8 <sup>†</sup>        | 15                   | 2.2                  | 5.9                  |

| NEF                                                 |                         | <b>4.10</b> <sup>†</sup> | 3.76 <sup>†</sup>       | 4.31                 | 8.70                 | 5.87                 |

TABLE III Comparison Table

<sup>†</sup>Measured at 38°C \*Not Available \*\*Not Applicable

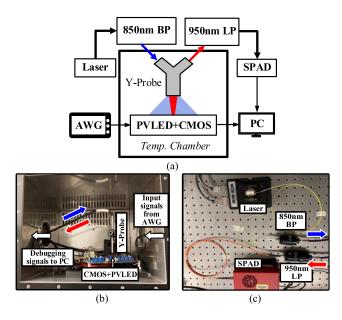

Fig. 15. (a) Wireless optical setup diagram. (b) Side view photograph of the wireless optical setup inside temperature chamber. (c) Top view photograph of the external light source and SPAD.

maintaining 38 °C. The amplifier achieves 68-dB peak gain with an SBP bandwidth range of 380–1060 Hz under  $150-\mu$ W/mm<sup>2</sup> NIR light, which is sufficient to amplify and filter hundreds of  $\mu V_{pk-to-pk}$  of input neural spike in interest and to fully utilize the available voltage headroom of the chip. The common-mode rejection ratio (CMRR) and power supply rejection ratio (PSRR) were higher than 67 dB. The measured input-referred noise (IRN) was 6.2  $\mu V_{rms}$ . The difference of the measured performance was negligible when the 850-nm

Fig. 16. Measured local programming with the fully wireless optical setup.

NIR light source with the target NIR optical power density of 150  $\mu$ W/mm<sup>2</sup> is turned on and off (Fig. 12 and Table II). Fig. 13 shows the measured peak gain and  $f_{HP}$  across the NIR light intensity level for an  $R_{PSD}$ -based baseline and the proposed structure. While the baseline structure failed at 8  $\mu$ W/mm<sup>2</sup>, the proposed structure remained stable up to 300  $\mu$ W/mm<sup>2</sup>.

Fig. 14 shows the measured transient waveform of the fully functioning AFE with the  $300-\mu$ W/mm<sup>2</sup> NIR light turned on. The pre-recorded motor cortex signal of a monkey was streamed into the chip using an arbitrary waveform generator (AWG; Keysight, 33600A) and a 1000-to-1 on-printed circuit board (PCB) attenuator. AMPOUT at the second row is the output of the amplifier and, at the same time, the input of the SBP extraction unit. P<sub>[0-2]</sub> and N<sub>[0-2]</sub> are the outputs of the six pulse generators in Fig. 7. The LED\_EN signal is the final output of the SBP extraction unit. The proposed computing unit consumed 29.5 nW in simulation while occupying only 0.045 mm<sup>2</sup>.

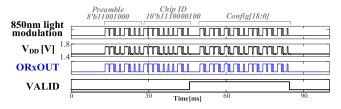

#### B. Wireless Optical Measurement

To validate the wireless optical function, the proposed IC was wire bonded to the custom PV/LED GaAs chip [19]

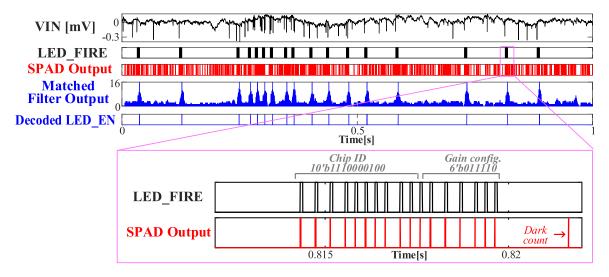

Fig. 17. Measured data uplink with the fully wireless optical setup.

and measured with the fully wireless optical setup including 850-nm laser (QFLD850200S, Qphotonics) for NIR powering and data downlink. An SPAD detector was used for uplink reception (SPDOEMNIR, Aurea) (Fig. 15). The measured transient waveform of the optical downlink using PWM of the external light is presented in Fig. 16. The  $V_{DD}$  node was monitored through the on-board analog buffer and plotted in the second row of Fig. 16 while modulating 850-nm light intensity between 500 and 0  $\mu$ W/mm<sup>2</sup>. Note that CDR (32 ms for CR and 70 ms for DR) occurs only once at start-up or very infrequently staying most of time in nominal operation phase under 150  $\mu$ W/mm<sup>2</sup>; therefore, 500- $\mu$ W/mm<sup>2</sup> peak modulation density for CDR does not impact tissue overheating. ORx captures and translates the  $V_{DD}$  modulation into the digital signal. When it detects the 18-b local programming passcode (8-b preamble + 10-b chipID), the VALID signal rises, and the data recovery of the 19-b chip configuration is executed.

With the identical optical setup in Fig. 15, the wireless data uplink functionality was validated (Fig. 17). The pre-recorded motor cortex signal of a monkey was streamed into the chip using an AWG (Keysight, 33600A) and a 1000-to-1 on-PCB attenuator (plotted as VIN in Fig. 17) to set the amplitude of the neural signal before amplification. LED FIRE in the second row of Fig. 17 is the chip internal signal that triggers the firing of the PGM LED packets (Fig. 9); the time interval between adjacent packets was inversely proportional to the average SBP. In other words, when there is active neural activity, the LED packets are fired more frequently. The internal LED\_FIRE signal was measured through the digital monitoring buffer as a baseline to validate the wirelessly measured uplink signal. The SPAD output (the third row in Fig. 17) is the measured photon detection result from the SPAD detector, including true photon counts received from the actual LED and the intrinsic dark counts (Fig. 17). Using the 16-b-PGM LED pattern, the wirelessly measured SPAD Output was matched filtered in MATLAB, and the decoded LED\_EN in the last row in Fig. 17 matched exactly with the baseline (LED\_FIRE), successfully rejecting the dark counts.

Fig. 18. (a) *In vivo* measurement setup photograph. (b) Setup diagram. (c) Measured transient waveform.

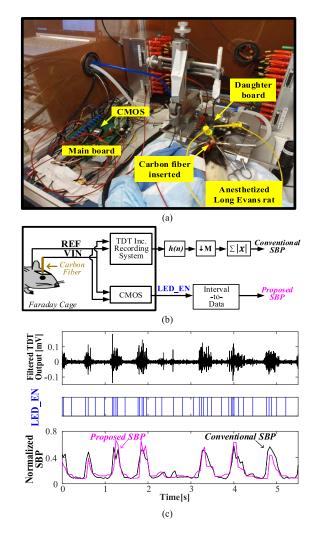

# C. In Vivo Measurement

All procedures complied with the guidelines of the University of Michigan's Institutional Animal Care and Use

Fig. 19. Finger movement decoding result. (a) Predicted finger position and velocity. (b) Average LED firing rate histogram. (c) Position and velocity prediction accuracy.

Committee. The AFE functionality was verified in vivo using a carbon fiber inserted into the motor cortex of an anesthetized Long Evans rat [Fig. 18(a) and (b)]. A bare carbon fiber  $(d = 6.8 \ \mu m)$  was mounted on a daughter PCB using silver epoxy. The fiber was then Parylene C coated (t = 800 nm), the tip re-exposed, and coated with PEDOT:pTS to lower the impedance. The inserted carbon fiber was electrically connected to the input [VIN in Fig. 18(b)] of the proposed chip on a motherboard and a commercial high-power neural recording system (RA 16AC headstage, RA16PA pre-amp and RX7 stimulator base station, TDT Inc.) simultaneously. A bone screw, serving as ground for both recording systems, was placed at the most posterior portion of the skull and was also electrically connected to the proposed IC and the commercial recording system in parallel [REF in Fig. 18(b)]. The proposed SBP was decoded from the time interval of the measured LED\_EN signal, while the conventional SBP was calculated in MATLAB using the raw data acquired by the commercial recording system (high-pass filtered at 2.2 Hz by the headstage, anti-aliased filtered at 7.5 kHz, and sampled at 24.414 kHz). The SBP acquired using the proposed IC achieved a correlation coefficient of 0.797 to the conventional SBP.

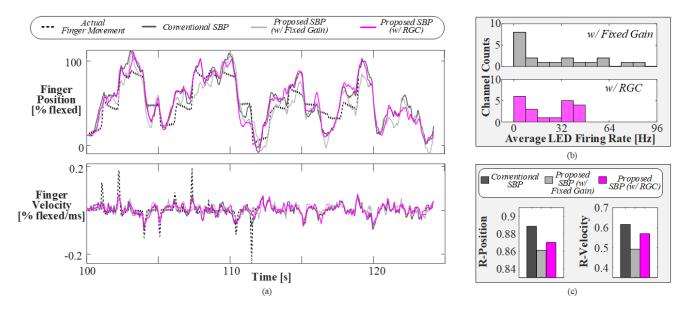

# D. Motor Prediction With the Pre-Recorded Neural Signal

The 1-D finger position and velocity of a monkey were predicted using a 20-channel prerecorded motor cortex signal and the resulting SBP from the IC with both fixed gain and off-chip RGC (Fig. 19). A Kalman filter (KF) was used for training and prediction [21]–[23]. The first 100 s of the measured SBP and prerecorded finger movement was used for training, and the next 24 s of the finger movement was predicted with the trained KF and the measured SBP. In Fig. 19, three predicted finger positions are compared with the actual finger movement. The conventional SBP was

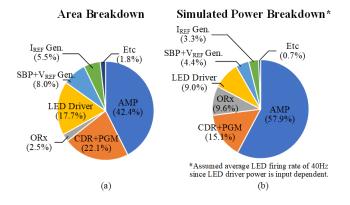

Fig. 20. (a) Area and (b) simulated power breakdown.

obtained from bandpass filtering and absolute averaging on the raw prerecorded neural signal measured from a highpower analog front end in MATLAB [21]-[23]. The proposed SBP measured by the chip successfully predicts the finger position/velocity with a correlation coefficient of 0.864/0.492 with a fixed gain configuration across 20 channels, indicating only small accuracy degradation compared to the high-power conventional SBP method achieving 0.889/0.616 [Fig. 19(c)]. With the RGC, the gain configuration of each channel case was updated to optimize the average LED firing rate by increasing the gain for the channel case when the average LED firing rate was too low and vice versa [Fig. 19(b)]. With the offchip RCG, the proposed SBP achieved a prediction correlation coefficient of 0.870/0.569 [Fig. 19(c)], and the LED firing rate remained below 50 Hz across all the channels, allowing for increased channel utilization.

# V. CONCLUSION

This article proposes a light-tolerant wireless neural recording IC for motor prediction with NIR-based power and data telemetry, addressing a unique challenge of light-robust lowpower circuit design. The proposed IC can fully function under 300  $\mu$ W/mm<sup>2</sup> of light exposure, due to its  $R_{PSD}$ -less AFE design and novel digital SBP extractor, whereas other stateof-the-art optical-based standalone recorders [15], [16] do not consider light tolerance in their designs. The proposed recorder achieves the lowest power consumption of 0.57  $\mu$ W at 38 °C with 4.1 noise efficiency factor (NEF) with an active area of 0.19 mm  $\times$  0.28 mm (Table III, Fig. 20). The IC supports optical powering and bi-directional data telemetry along with a vertical stacked dual-junction PV and LED GaAs chip [19]; 11 pF of on-chip MIM decoupling capacitors and 27 pF of intrinsic PV cell capacitance minimize random fluctuation of  $V_{DD}$ , while AFE achieves high PSRR above 67 dB to prevent power supply noise coupling. SBP, the neural feature of interest, is on-chip extracted and fired out to a repeater through the custom LED with PGM-SIM uplink signal. The data downlink is performed by PWM optical modulation, while sufficient hysteresis voltage ( $V_{IH}-V_{IL}$ , 91 mV, simulated) of the ORx and hardwired passcode in CDR prevents false trigger and false data downlink from random  $V_{DD}$  fluctuation. In addition, the RGC capability with the individual mote downlink provides the potential for future systematic optimization (i.e., off-chip AGC) of the channel utilization and decoding accuracy when multiple motes are implanted. We expect full integration of the implantable floating mote with the proposed IC and other components in the future, enabling true wireless long-term neural recording with minimum risk of brain tissue damage.

## REFERENCES

- R. A. Normann, E. M. Maynard, P. J. Rousche, and D. J. Warren, "A neural interface for a cortical vision prosthesis," *Vis. Res.*, vol. 39, no. 15, pp. 2577–2587, Jul. 1999.

- [2] G. Buzsáki et al., "Tools for probing local circuits: High-density silicon probes combined with optogenetics," *Neuron*, vol. 86, no. 1, pp. 92–105, Apr. 2015.

- [3] G. Rios, E. V. Lubenov, D. Chi, M. L. Roukes, and A. G. Siapas, "Nanofabricated neural probes for dense 3-D recordings of brain activity," *Nano Lett.*, vol. 16, no. 11, pp. 6857–6862, Nov. 2016.

- [4] J. J. Jun et al., "Fully integrated silicon probes for high-density recording of neural activity," *Nature*, vol. 551, no. 7679, pp. 232–236, Nov. 2017.

- [5] M. D. Ferro *et al.*, "NeuroRoots, a bio-inspired, seamless brain machine interface device for long-term recording," *BioRxiv*, Jan. 2018. [Online]. Available: https://www.biorxiv.org/about/FAQ, doi: 10.1101/460949.

- [6] J.-W. Jeong, G. Shin, S. I. Park, K. J. Yu, L. Xu, and J. A. Rogers, "Soft materials in neuroengineering for hard problems in neuroscience," *Neuron*, vol. 86, no. 1, pp. 175–186, Apr. 2015.

- [7] E. Musk, "An integrated brain-machine interface platform with thousands of channels," *BioRxiv*, Jan. 2019. [Online]. Available: https://www.biorxiv.org/about/FAQ, doi: 10.1101/703801.

- [8] C. M. Lopez *et al.*, "A neural probe with up to 966 electrodes and up to 384 configurable channels in 0.13 μm SOI CMOS," *IEEE Trans. Biomed. Circuits Syst.*, vol. 11, no. 3, pp. 510–522, Jun. 2017.

- [9] B. C. Johnson *et al.*, "An implantable 700 μW 64-channel neuromodulation IC for simultaneous recording and stimulation with rapid artifact recovery," in *Proc. Symp. VLSI Circuits*, Jun. 2017, pp. C48–C49.

- [10] H. Chandrakumar and D. Marković, "An 80-mVpp linear-input range, 1.6-GΩ input impedance, low-power chopper amplifier for closed-loop neural recording that is tolerant to 650-mVpp common-mode interference," *IEEE J. Solid-State Circuits*, vol. 52, no. 11, pp. 2811–2828, Nov. 2017.

- [11] C. Kim, S. Joshi, H. Courellis, J. Wang, C. Miller, and G. Cauwenberghs, "A 92 dB dynamic range sub-μV<sub>rms</sub>-noise 0.8μW/ch neural-recording ADC array with predictive digital autoranging," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2018, pp. 470–472.

- [12] J. Lee *et al.*, "Wireless power and data link for ensembles of sub-mm scale implantable sensors near 1 GHz," in *Proc. IEEE Biomed. Circuits Syst. Conf. (BioCAS)*, Oct. 2018, pp. 1–4.

- [13] J. Lee et al., "An implantable wireless network of distributed microscale sensors for neural applications," in Proc. 9th Int. IEEE/EMBS Conf. Neural Eng. (NER), Mar. 2019, pp. 871–874.

- [14] M. M. Ghanbari *et al.*, "A sub-mm<sup>3</sup> ultrasonic free-floating implant for multi-mote neural recording," *IEEE J. Solid-State Circuits*, vol. 54, no. 11, pp. 3017–3030, Nov. 2019.

- [15] S. Lee, A. J. Cortese, A. P. Gandhi, E. R. Agger, P. L. McEuen, and A. C. Molnar, "A 250 μm × 57 μm microscale opto-electronically transduced electrodes (MOTEs) for neural recording," *IEEE Trans. Biomed. Circuits Syst.*, vol. 12, no. 6, pp. 1256–1266, Dec. 2018.

- [16] J. Lim et al., "A 0.19×0.17 mm<sup>2</sup> wireless neural recording IC for motor prediction with near-infrared-based power and data telemetry," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2020, pp. 416–418.

- [17] K. Yang, Q. Dong, D. Blaauw, and D. Sylvester, "A 553F<sup>2</sup> 2-transistor amplifier-based physically unclonable function (PUF) with 1.67% native instability," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2017, pp. 146–147.

- [18] P. R. Patel *et al.*, "Chronic *in vivo* stability assessment of carbon fiber microelectrode arrays," *J. Neural Eng.*, vol. 13, no. 6, Dec. 2016, Art. no. 066002.

- [19] E. Moon *et al.*, "Bridging the 'last millimeter' gap of brain-machine interfaces via near-infrared wireless power transfer and data communications," *ACS Photon.*, vol. 8, no. 5, pp. 1430–1438, Apr. 2021.

- [20] J. Lim *et al.*, "A light tolerant neural recording IC for near-infraredpowered free floating motes," in *Proc. Symp. VLSI Circuits*, Jun. 2021, pp. 1–2.

- [21] Z. T. Irwin *et al.*, "Enabling low-power, multi-modal neural interfaces through a common, low-bandwidth feature space," *IEEE Trans. Neural Syst. Rehabil. Eng.*, vol. 24, no. 5, pp. 521–531, May 2016.

- [22] Z. T. Irwin *et al.*, "Neural control of finger movement via intracortical brain-machine interface," *J. Neural Eng.*, vol. 14, no. 6, Dec. 2017, Art. no. 066004.

- [23] S. R. Nason *et al.*, "A low-power band of neuronal spiking activity dominated by local single units improves the performance of brain–machine interfaces," *Nature Biomed. Eng.*, vol. 4, no. 10, pp. 973–983, Oct. 2020.

- [24] P. Rappaport, "The photovoltaic effect and its utilization," Sol. Energy, vol. 3, no. 4, pp. 8–18, Dec. 1959.

- [25] R. Corkish, M. A. Green, M. E. Watt, and S. R. Wenham, "The behaviour of solar cells," in *Applied Photovoltaics, Revised*, vol. 2. Oxfordshire, U.K.: Routledge, 2013, ch.3, sec.3, p. 48.

- [26] S. Wang, C. M. Lopez, M. Ballini, and N. V. Helleputte, "Leakage compensation scheme for ultra-high-resistance pseudo-resistors in neural amplifiers," *Electron. Lett.*, vol. 54, no. 5, pp. 270–272, Mar. 2018.

- [27] N. Verma, A. Shoeb, J. Bohorquez, J. Dawson, J. Guttag, and A. P. Chandrakasan, "A micro-power EEG acquisition SoC with integrated feature extraction processor for a chronic seizure detection system," *IEEE J. Solid-State Circuits*, vol. 45, no. 4, pp. 804–816, Apr. 2010.

- [28] T. Jang *et al.*, "A noise-efficient neural recording amplifier using discrete-time parametric amplification," *IEEE Solid-State Circuits Lett.*, vol. 1, no. 11, pp. 203–206, Nov. 2018.

- [29] M. Seok, G. Kim, D. Blaauw, and D. Sylvester, "A portable 2-transistor picowatt temperature-compensated voltage reference operating at 0.5 V," *IEEE J. Solid-State Circuits*, vol. 47, no. 10, pp. 2534–2545, Oct. 2012.

**Jongyup Lim** (Member, IEEE) received the B.S. degree (*summa cum laude*) in electrical and computer engineering from Seoul National University, Seoul, South Korea, in 2016, and the M.S. and Ph.D. degrees in electrical and computer engineering from the University of Michigan, Ann Arbor, MI, USA, in 2018 and 2021, respectively.

During his Ph.D. degree, he interned at Apple, Cupertino, CA, USA. His research interests include wireless neural recording systems, energy-efficient deep learning hardware, clock generation, and

ultralow-power sensor node design.

Dr. Lim was a recipient of the Doctoral Fellowship from the Kwanjeong Educational Foundation in South Korea.

**Jungho Lee** (Graduate Student Member, IEEE) received the B.S. and M.S. degrees in electrical engineering from the Pohang University of Science and Technology (POSTECH), Pohang, South Korea, in 2018 and 2020, respectively. He is currently pursuing the Ph.D. degree with the University of Michigan, Ann Arbor, MI, USA.

His research interests include brain-machine interface, wireless neural recorder, and neuroprosthetic stimulator.

**Eunseong Moon** (Member, IEEE) received the B.S. degree in electrical engineering from Chung-Ang University, Seoul, South Korea, in 2012, and the M.S. and Ph.D. degrees in electrical engineering from the University of Michigan, Ann Arbor, MI, USA, in 2020.

He was a Post-Doctoral Researcher with the University of Michigan. After his studies, he has been working at ASML, Inc., San Jose, CA, USA, where he is currently a Senior Design Engineer.

Michael Barrow (Graduate Student Member, IEEE) received the B.S.E.E. degree from Purdue University, West Lafayette, IN, USA, in 2015, and the Ph.D. degree from the University of Michigan, Ann Arbor, MI, USA, in 2021.

Since 2021, he has been a Post-Doctoral Researcher at the University of Maryland, College Park, MD, USA, and the Laboratory for Physical Sciences. His research interests include integrated photonics, optical metasurfaces, and microelectronic fabrication.

Gabriele Atzeni (Graduate Student Member, IEEE) received the B.S. degree in electrical engineering and the M.S. degree in electronics engineering from the University of Cagliari, Cagliari, Italy, in 2016 and 2018, respectively. He is currently pursuing the Ph.D. degree in information technology and electrical engineering with ETH Zürich, Zürich, Switzerland.

From 2017 to 2018, he was with Columbia University, New York, NY, USA, working at the Columbia Integrated Systems Laboratory under the supervision

of Prof. Peter Kinget. In 2018, he joined the Energy-Efficient Circuits and IoT Systems Group led by Prof. Taekwang Jang, ETH Zürich. His research interests include front-end architectures, wireless power transfer, and RF communication systems for fully wireless brain-machine interfaces and biomedical systems.

Mr. Atzeni was a co-recipient of the International Solid-State Circuits Conference (ISSCC) 2021 Jan Van Vessem Award for Outstanding European Paper.

faces. His research reaction of electrode over time.

**Joseph G. Letner** received the bachelor's and master's degrees in biomedical engineering with a minor in electrical engineering from the University of Michigan, Ann Arbor, MI, USA, in 2015 and 2016, respectively, where he is currently pursuing the Ph.D. degree with the Department of Biomedical Engineering advised by Dr. Cynthia Chestek and Dr. Dawen Cai.

His research is focused on fabrication and implantation techniques of novel carbon fiber neural electrodes for use in brain–machine interresearch also focuses on characterizing the biological electrode implantation and improving recording capability

**Joseph T. Costello** received the B.S. degree (*summa* cum laude) in electrical engineering from the University of Michigan, Ann Arbor, MI, USA, in 2020, where he is currently pursuing the Ph.D. degree in electrical engineering.

His research interests include low-power brainmachine interfaces, neural decoding algorithms, and restoration of fine motor control.

Mr. Costello was awarded a fellowship from the National Science Foundation Graduate Research Fellowship Program in 2020.

Samuel R. Nason received the B.S. degree (summa cum laude) in electrical engineering from the University of Florida, Gainesville, FL, USA, in 2016, and the M.S. degree in biomedical engineering from the University of Michigan, Ann Arbor, MI, USA, in 2018, where he is currently pursuing the Ph.D. degree under the supervision of Dr. Cindy Chestek. His dissertation focuses on low-power brain–machine interface technologies for restoring function to paralyzed fingers using function.

Mr. Nason was awarded an F31 predoctoral fellowship from the National Institutes of Health and received the 2021 Towner Prize for Outstanding Ph.D. Research at the College of Engineering, University of Michigan, for his dissertation work.

**Paras R. Patel** received the B.S. degree in bioengineering from the University of California at Berkeley, Berkeley, CA, USA, in 2007, and the M.S.E. and Ph.D. degrees in biomedical engineering from the University of Michigan, Ann Arbor, MI, USA, in 2010 and 2015, respectively.

He is currently an Assistant Research Scientist with the University of Michigan.

Yi Sun received the B.S. and Ph.D. degrees in optical engineering from the Huazhong University of Science and Technology, Wuhan, China, in 2010 and 2016, respectively.

He worked as an Optical Engineer at Accelink Technologies, Wuhan, from 2017 to 2018 and a Research Fellow at the University of Michigan, Ann Arbor, MI, USA, from 2018 to 2021. He is currently a Senior Research Fellow with the University of Michigan. His current research interests focus on III–V optoelectronic devices, including laser diodes,

micro-light-emitting diodes (LEDs), and photovoltaics.

**Parag G. Patil** received the B.S. degree in electrical engineering and computer science from the Massachusetts Institute of Technology, Cambridge, MA, USA, in 1989, the M.A. degree in philosophy and economics from the University of Oxford, Oxford, U.K., in 1991, and the M.D. Ph.D. degree in biomedical engineering from Johns Hopkins University, Baltimore, MD, USA, in 1999. He completed neurosurgery residency at Duke University, Durham, NC, USA, in 2005, and stereotactic and functional neurosurgery fellowship at the University of Toronto,

Toronto, ON, Canada, in 2006.

He joined the faculty at the University of Michigan in 2005. After graduation, he was awarded a Marshall Scholarship to study philosophy and economics at the Magdalen College, Oxford University. He is currently an Associate Professor of neurosurgery, neurology, anesthesiology, and biomedical engineering. His academic goal is to utilize engineering and mathematical techniques, along with interdisciplinary collaboration, to improve neuroprosthetics and to perform translational neuroscience research.

Dr. Patil serves as the Associate Chair for Clinical and Translational Research and the Co-Director of the Neuroscience and Sensory Clinical Trial Support Unit (CTSU) and in a leadership role in diverse multidisciplinary, multi-investigator research efforts. He received a fellowship at the University of Toronto.

STATE CIRCUITS LETTERS.

Hun-Seok Kim (Member, IEEE) received the B.S. degree in electrical engineering from Seoul National University, Seoul, South Korea, in 2001, and the Ph.D. degree in electrical engineering from the University of California at Los Angeles (UCLA), Los Angeles, CA, USA, in 2010.

He is currently an Assistant Professor with the University of Michigan, Ann Arbor, MI, USA. His research focuses on system analysis, novel algorithms, and VLSI architectures for lowpower/high-performance wireless communications, signal processing, computer vision, and machine learning systems.

Dr. Kim was a recipient of the DARPA Young Faculty Award in 2018 and the NSF CAREER Award in 2019. He is an Associate Editor of IEEE TRANSACTIONS ON MOBILE COMPUTING, IEEE TRANSACTIONS ON GREEN COMMUNICATIONS AND NETWORKING, and the IEEE SOLID-

**Cynthia A. Chestek** (Member, IEEE) received the B.S. and M.S. degrees in electrical engineering from Case Western Reserve University, Cleveland, OH, USA, in 2005, and the Ph.D. degree in electrical engineering from Stanford University, Stanford, CA, USA, in 2010.

She joined the faculty of the University of Michigan, Ann Arbor, MI, USA, in 2012, where she is currently an Associate Professor of biomedical engineering. She runs the Cortical Neural Prosthetics Laboratory, which focuses on brain and nerve

control of finger movements as well as high-density carbon fiber electrode arrays. She is the author of 58 full-length scientific articles. Her research interests include high-density interfaces to the nervous system for the control of multiple-degree-of-freedom hand and finger movements.

Jamie Phillips (Senior Member, IEEE) received the B.S., M.S., and Ph.D. degrees in electrical engineering from the University of Michigan, Ann Arbor, MI, USA, in 1994, 1996, and 1998, respectively.

He was a Post-Doctoral Researcher at Sandia National Laboratories, Albuquerque, NM, USA, from 1998 to 1999, and a Research Scientist at the Rockwell Science Center, Tousand Oaks, CA, USA, from 1999 to 2001. He joined the faculty of the Department of Electrical Engineering and Computer Science, University of Michigan, in 2002, where he

was an Arthur F. Thurnau Professor. He joined the University of Delaware, Newark, DE, USA, in 2020, as a Professor and the Chair of the Department of Electrical and Computer Engineering. His technical interests and contributions are in the areas of compound semiconductor materials and optoelectronic devices. He has published more than 150 peer-reviewed journal articles on these subjects.

Dr. Phillips is a member of the American Society for Engineering and Education (ASEE) and the Materials Research Society (MRS). He received the NSF CAREER Award in 2003 and the DARPA MTO Young Faculty Award in 2007. He currently serves as an Associate Editor for the IEEE TRANSACTIONS ON ELECTRON DEVICES and the Chair for the IEEE Electron Devices Society Optoelectronics Technical Committee.

**David Blaauw** (Fellow, IEEE) received the B.S. degree in physics and computer science from Duke University, Durham, NC, USA, in 1986, and the Ph.D. degree in computer science from the University of Illinois at Urbana–Champaign, Champaign, IL, USA, in 1991.

Until August 2001, he worked with Motorola, Inc., Austin, TX, USA, where he was the Manager of the High Performance Design Technology Group. Since August 2001, he has been the Faculty Member with the University of Michigan, Ann Arbor, MI,

USA, where he is currently the Kensall D. Wise Collegiate Professor of Electrical Engineering and Computer Science. He is also the Director of the Michigan Integrated Circuits Laboratory. He has published over 600 articles and holds 65 patents. He has researched on ultralow-power wireless sensors using subthreshold operation and low-power analog circuit techniques for millimeter systems. This research was awarded the MIT Technology Review's "one of the year's most significant innovations." His research group introduced the so-called near-threshold computing, which has become a common concept in semiconductor design. Most recently, he has pursued research in cognitive computing using analog, in-memory neural networks for edge devices, and genomics for precision health.

Dr. Blaauw was a member of the IEEE International Solid-State Circuits Conference (ISSCC) Analog Program Subcommittee and the General Chair of the IEEE International Symposium on Low Power Electronics and Design. He received numerous best paper awards, the Motorola Innovation Award, and the 2016 SIA-SRC Faculty Award for lifetime research contributions to the U.S. semiconductor industry.

**Dennis Sylvester** (Fellow, IEEE) received the Ph.D. degree in electrical engineering from the University of California at Berkeley, Berkeley, CA, USA, in 1999.

He held research staff positions at Synopsys, Mountain View, CA, USA, and Hewlett-Packard Laboratories, Palo Alto, CA, USA, as well as visiting professorships at the National University of Singapore, Singapore, and Nanyang Technological University, Singapore. He is currently the Edward S. Davidson Collegiate Professor of Electrical and

Computer Engineering at the University of Michigan, Ann Arbor, MI, USA. His research has been commercialized via three major venture capital-funded start-up companies: Ambiq Micro, Austin, TX, USA, Cubeworks, Ann Arbor, and Mythic, Redwood City, CA, USA. His main research interests are in the design of miniaturized ultralow-power microsystems, touching on analog, mixed-signal, and digital circuits. He has published over 500 articles and holds more than 50 U.S. patents in these areas.

Dr. Sylvester is a member of the Administrative Committee of the IEEE Solid-State Circuits Society and an Associate Editor of IEEE JOURNAL OF SOLID-STATE CIRCUITS. He was a Distinguished Lecturer of the IEEE Solid-State Circuits Society. He has received 14 best paper awards and nominations and was named a Top Contributing Author at the International Solid-State Circuits Conference (ISSCC) and the most prolific author at the IEEE Symposium on Very Large Scale Integration (VLSI) Circuits.

Taekwang Jang (Senior Member, IEEE) received the B.S. and M.S. degrees in electrical engineering from the Korea Advanced Institute of Science and Technology (KAIST), Daejeon, South Korea, in 2006 and 2008, respectively, and the Ph.D. degree from the University of Michigan, Ann Arbor, MI, USA, in 2017. His dissertation was titled "Circuit and System Designs for Millimeter-Scale IoT and Wireless Neural Recording."

From 2008 to 2013, he worked at Samsung Electronics Company Ltd., Yongin, South Korea,

focusing on mixed-signal circuit design, including analog and all-digital phase-locked loops for communication systems and mobile processors. After working as a Post-Doctoral Research Fellow at the University of Michigan, he joined the ETH Zürich, Zürich, Switzerland, in 2018, as an Assistant Professor and is leading the Energy-Efficient Circuits and IoT Systems Group. His research interests include ultralow-power systems, biomedical circuits, frequency synthesizers, and data converters.

Dr. Jang is a member of the Competence Center for Rehabilitation Engineering and Science and the Chair of IEEE Solid-State Circuits Society, Switzerland Chapter. He was a co-recipient of IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS 2009 Guillemin-Cauer Best Paper Awards.